# Advances in Microelectronics: Reviews

# Volume 3

Sergey Y. Yurish Editor

# **Advances in Microelectronics: Reviews**

**Book Series, Volume 3**

Sergey Y. Yurish *Editor*

Advances in Microelectronics: Reviews, Volume 3

Published by International Frequency Sensor Association (IFSA) Publishing, S. L., 2021 E-mail (for print book orders and customer service enquires): ifsa.books@sensorsportal.com

Visit our Home Page on http://www.sensorsportal.com

Advances in Microelectronics: Reviews, Vol. 3 is an open access book which means that all content is freely available without charge to the user or his/her institution. Users are allowed to read, download, copy, distribute, print, search, or link to the full texts of the articles, or use them for any other lawful purpose, without asking prior permission from the publisher or the authors. This is in accordance with the BOAI definition of open access.

Neither the authors nor International Frequency Sensor Association Publishing accept any responsibility or liability for loss or damage occasioned to any person or property through using the material, instructions, methods or ideas contained herein, or acting or refraining from acting as a result of such use.

ISBN: 978-84-09-33338-7 e-ISBN: 978-84-09-33339-4

BN-20210831-XX

BIC: TJFD

# Acknowledgments As Editor I would like to express my undying gratitude to all authors, editorial staff, reviewers and others who actively participated in this book. We want also to express our gratitude to all their families, friends and colleagues for their help and understanding.

# **Contents**

| Contents                                                             | 7  |

|----------------------------------------------------------------------|----|

| Contributors                                                         |    |

| Preface                                                              |    |

| 1101000                                                              |    |

| 1. Organic Electronic Materials and Devices                          | 19 |

|                                                                      |    |

| 1.1. Introduction                                                    |    |

| 1.2. Charge Transport Phenomenon in Organic Semiconductors           |    |

| 1.3. Organic Field-Effect Transistor (OFET)                          |    |

| 1.3.1. History of OFET                                               |    |

| 1.3.2. How the OFET Works?                                           |    |

| 1.3.3. OFET Architecture                                             |    |

| 1.3.3.1. Horizontal Architecture                                     |    |

| 1.3.3.2. Vertical Architecture                                       |    |

| 1.3.4. Materials                                                     |    |

| 1.3.4.1. Substrates                                                  |    |

| 1.3.4.2. Insulator Layer                                             |    |

| 1.3.4.3. Semiconductor Layer                                         |    |

| 1.3.4.4. Electrodes                                                  |    |

| 1.3.5. Selected OFET Application                                     |    |

| 1.3.5.1. Controls Circuits                                           |    |

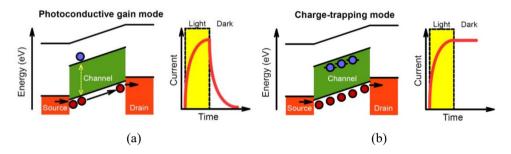

| 1.3.5.2. Non-volatile Memories                                       |    |

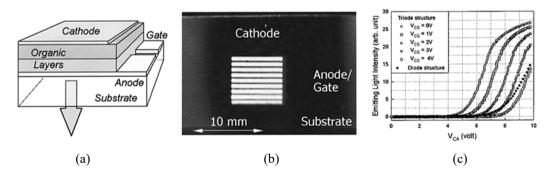

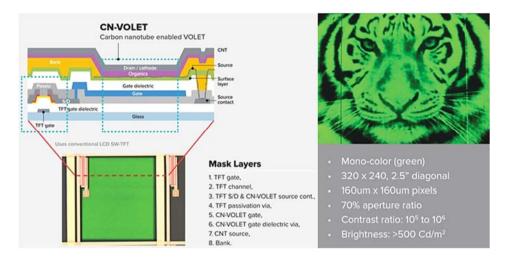

| 1.3.5.3. Lighting Devices (OLET – Organic Light-Emitting Transistor) |    |

| 1.3.5.4. Sensors                                                     | 48 |

| 1.4. Organic Light-Emitting Diode (OLED)                             | 50 |

| 1.4.1. Introduction                                                  | 50 |

| 1.4.2. What is an OLED?                                              |    |

| 1.4.3. Structures and Materials                                      |    |

| 1.4.4. Applications                                                  |    |

| 1.4.4.1. OLED Displays                                               | 55 |

| 1.4.4.2. OLED Lighting                                               |    |

| 1.4.4.3. Automotive                                                  |    |

| 1.5. Organic Solar Cells                                             | 57 |

| 1.6. Conclusion Remarks                                              |    |

|                                                                      |    |

| Acknowledgement                                                      |    |

| References                                                           | 63 |

|                                                                      | 1  |

| 2. Reconfigurable Conduction Mode in Bipolar Junction Transistor-ba  |    |

| Architectures for Recyclability                                      | 75 |

| 2.1. Introduction                                                    | 75 |

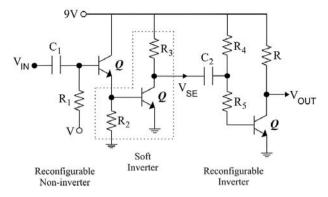

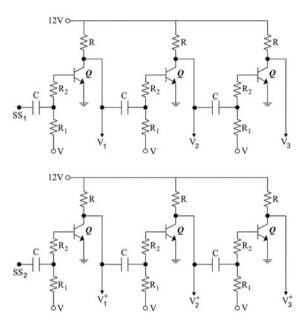

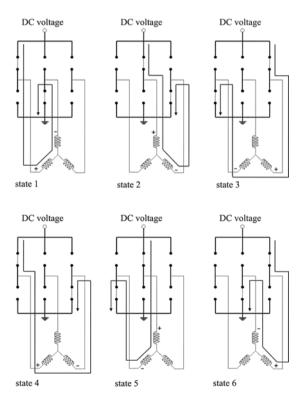

| 2.2. Reconfigurable Conduction Mode                                  | 77 |

| 2.2.1. Stability Analysis and Design Criteria                        |    |

| 2.2.2. Practical Examples                                            |    |

| •                                                                    |    |

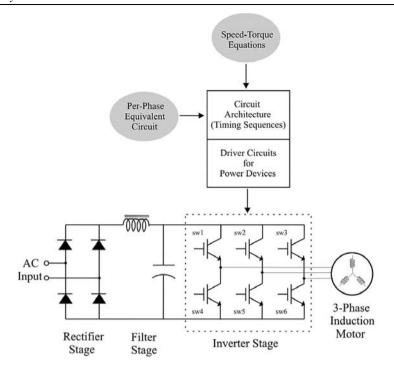

| 2.3. Circuit Architectures                                           |    |

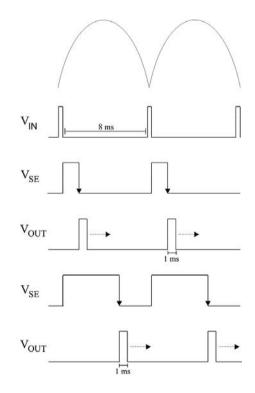

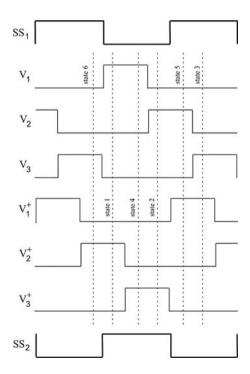

| 2.3.1. Time-shifted Pulses                                           |    |

| 2.3.2. Timing Sequences                                              | 85 |

| 2.4. Conclusions                                                                      |              |

|---------------------------------------------------------------------------------------|--------------|

| Acknowledgement                                                                       | 89           |

| References                                                                            | 90           |

| 3. Models and Techniques for Reliability Studies of Nano-scaled Interconnects         | 93           |

| 3.1. Introduction                                                                     | 93           |

| 3.1.1. Black's Equation                                                               |              |

| 3.1.2. Beyond Black's Equation                                                        | 96           |

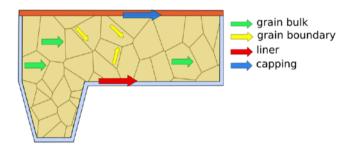

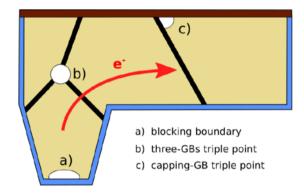

| 3.2. The Physics-BASED Modelling of Electromigration                                  | 96           |

| 3.2.1. Blech's Equation                                                               | 97           |

| 3.2.2. Effective Valence and Resistivity                                              |              |

| 3.2.3. Conditions for Void Nucleation                                                 | 98           |

| 3.3. Modelling of the Microstructure                                                  |              |

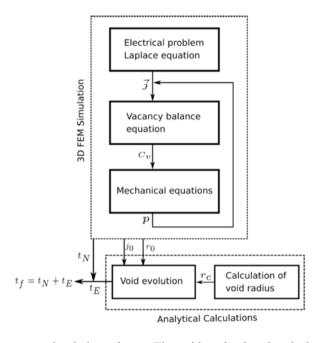

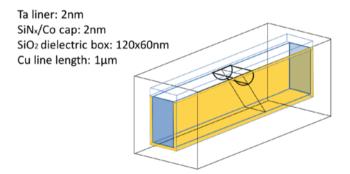

| 3.4. Analytical Model for Void Growth                                                 |              |

| 3.5. Estimation of Initial Void Size                                                  |              |

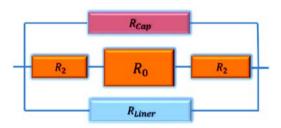

| 3.6. Resistance Calculation.                                                          |              |

| 3.7. Overall Scheme                                                                   | 105          |

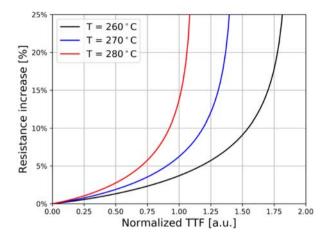

| 3.8. Simulation Results and Discussion                                                |              |

| 3.9. Conclusion.                                                                      |              |

| References                                                                            | 109          |

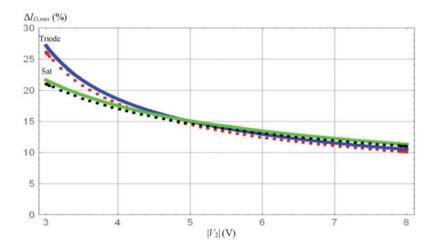

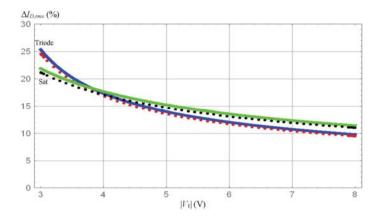

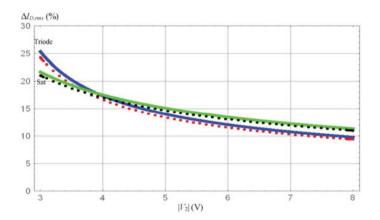

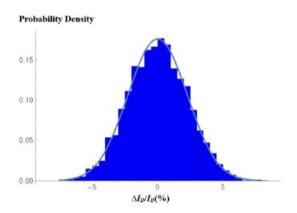

| 4. The Analytical Models of Random Variations in FGMOSFET                             | 113          |

| 4.1. Introduction                                                                     | 113          |

| 4.2. An Overview of FGMOSFET                                                          |              |

| 4.3. The Above 100 nm FGMOSFET Dedicated Models                                       |              |

| 4.4. The Nanometer FGMOSFET Dedicated Models                                          |              |

| 4.5. Concluding Remarks                                                               |              |

| References                                                                            |              |

| 5. Effective Young's Modulus of Electrodeposited Gold for Design                      |              |

| of MEMS Accelerometers                                                                | 149          |

| 5.1. Introduction                                                                     |              |

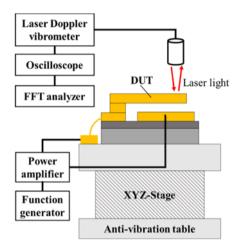

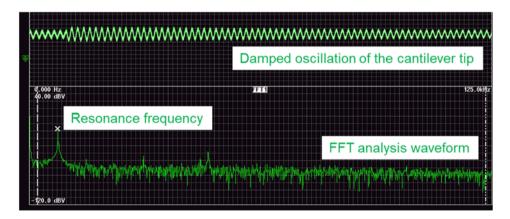

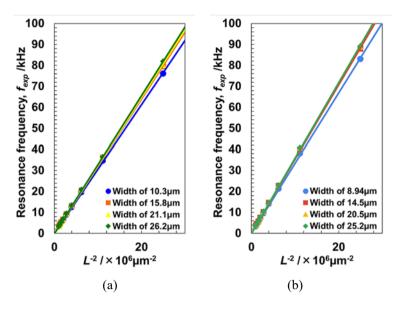

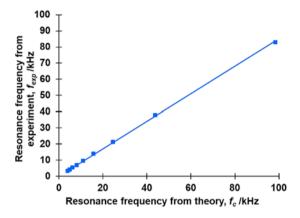

| 5.2. Effective Young's Modulus of Gold Micro-cantilevers by Resonance Frequency Metho | 149<br>d 151 |

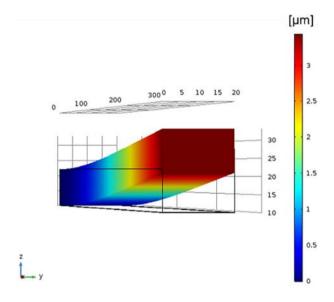

| 5.3. FEM Simulations of the Pure Gold Micro-cantilever                                |              |

| 5.4. Equation for Width Dependency of the Effective Young's Modulus                   |              |

| 5.5. Conclusions                                                                      |              |

| Acknowledgements                                                                      | 158          |

| References                                                                            |              |

|                                                                                       |              |

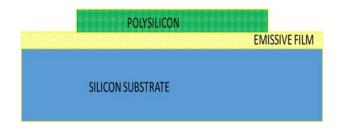

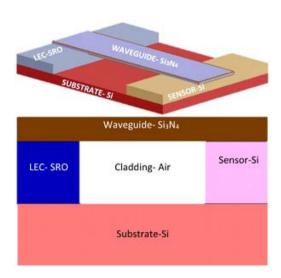

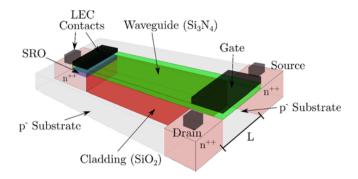

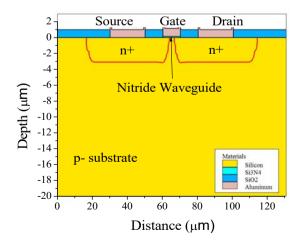

| 6. Sensor for Seamless Integrated Electrophotonics Circuits                           | 161          |

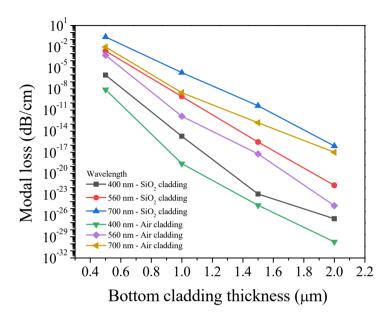

| 6.1. Introduction                                                                     | 161          |

| 6.2. Light Source                                                                     |              |

| 6.3. Optical Waveguide                                                                | 164          |

| 6.4. The Optical Sensor                                                               |              |

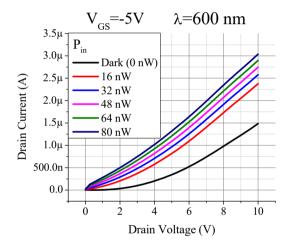

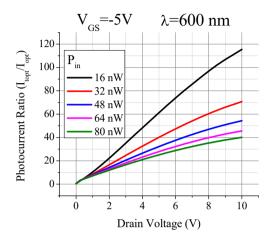

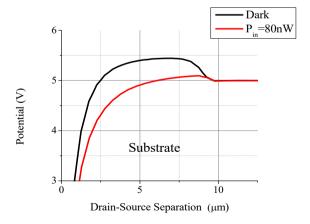

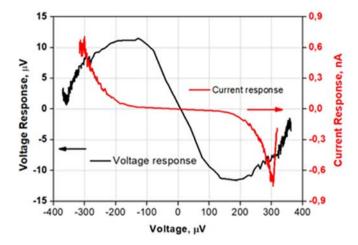

| 6.4.1. Optical and Electrical Behavior                                                |              |

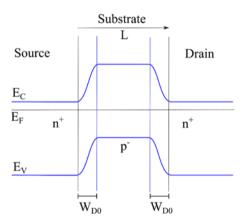

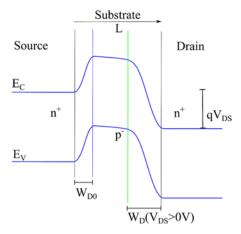

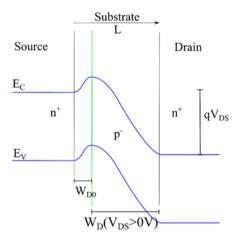

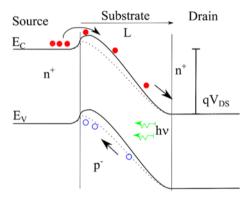

| 6.4.1.1 Electrical Behavior                                                           |              |

| 6.4.1.2. Physics of the Light Detection                                               |              |

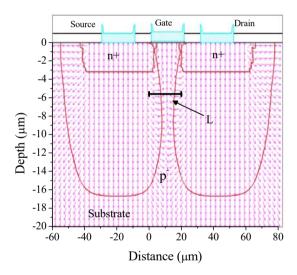

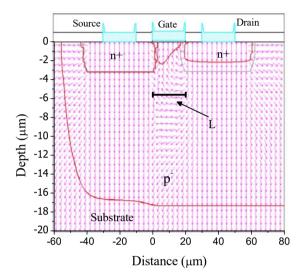

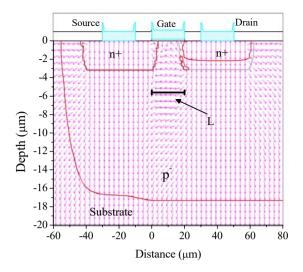

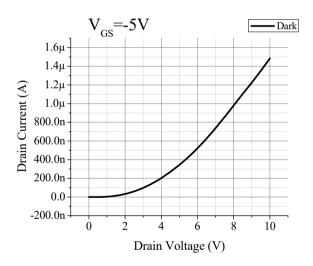

| 0.7.2. ETECTICAL - OPTICAL SIMULATION RESUITS                                         | 1 / 0        |

| 6.5. Conclusions                                                                                      | 178 |

|-------------------------------------------------------------------------------------------------------|-----|

| Acknowledgements                                                                                      | 178 |

| References.                                                                                           | 178 |

| 7. Fabrication of Aluminium Nanostructures for Microwave Detectors                                    |     |

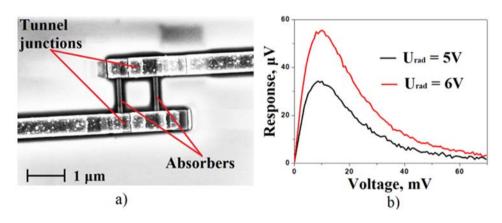

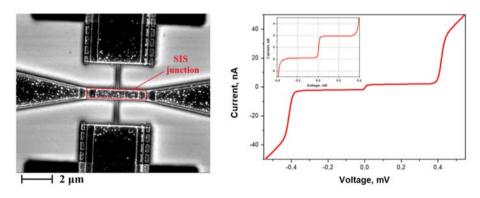

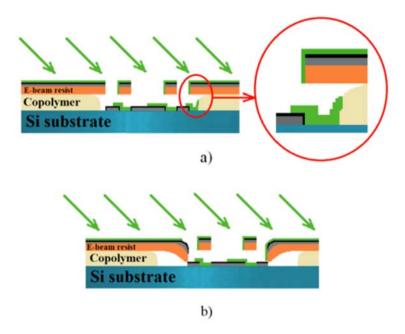

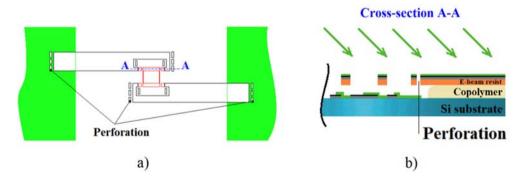

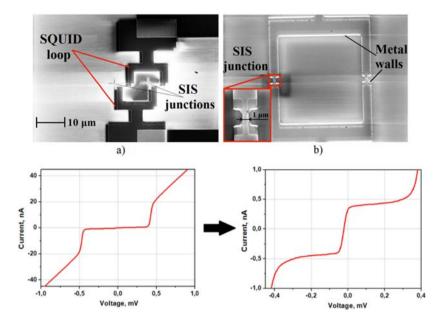

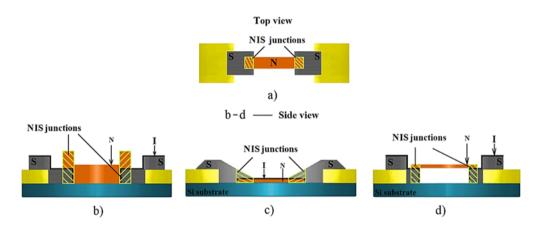

| Based on Tunnel Junctions                                                                             | 183 |

| 7.1. Introduction                                                                                     | 183 |

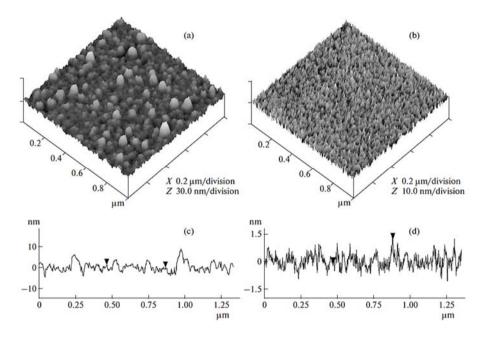

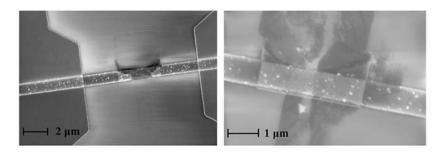

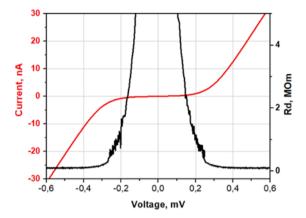

| 7.2. Investigation of Propertis of Thin Aluminum Films and Multylayer Structures  Based on Them       | 184 |

| 7.2.1. Granularity of Aluminum Film and Tunneling Junctions on Their Basis                            |     |

| 7.2.2. Superconductivity in Thin Aluminium Films and Multilayer Structures                            |     |

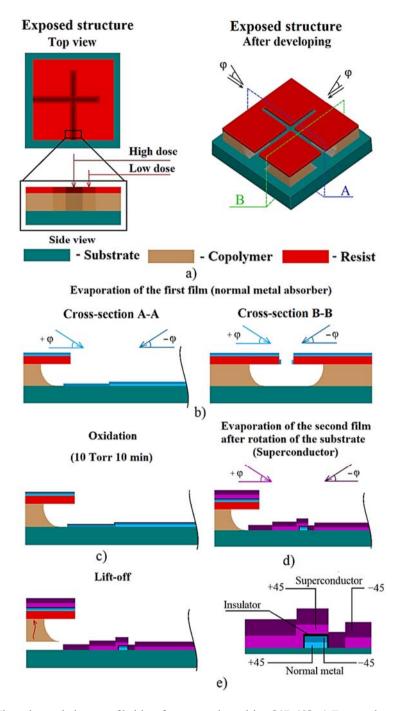

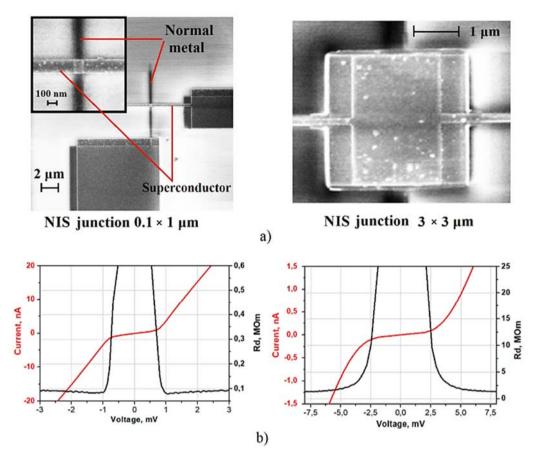

| 7.3. The Direct-write Technology                                                                      | 188 |

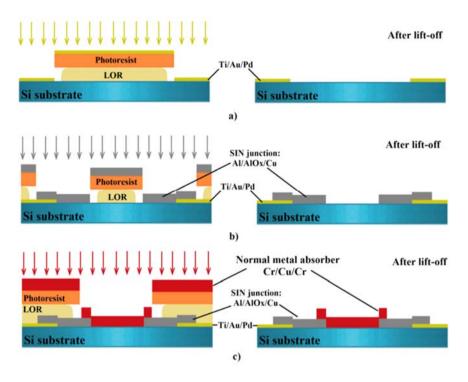

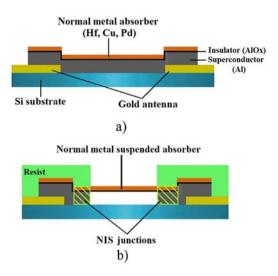

| 7.3.1. Simplest Technology                                                                            | 188 |

| 7.3.2. Direct-write Trilayer Technology                                                               |     |

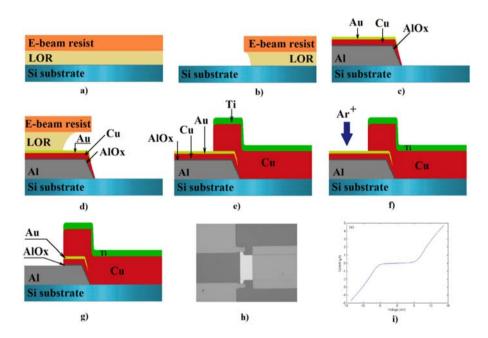

| 7.3.3. Sputtering with Separate Direct E-beam Lithography                                             |     |

| 7.4. The Dolan's Bridges                                                                              | 192 |

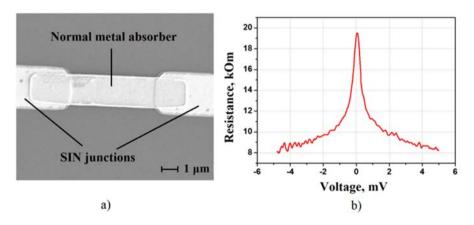

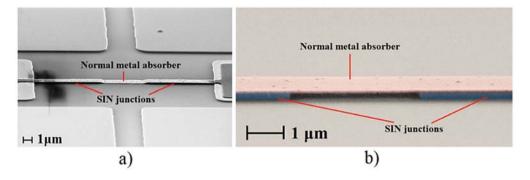

| 7.5. Bridge-free Technology                                                                           |     |

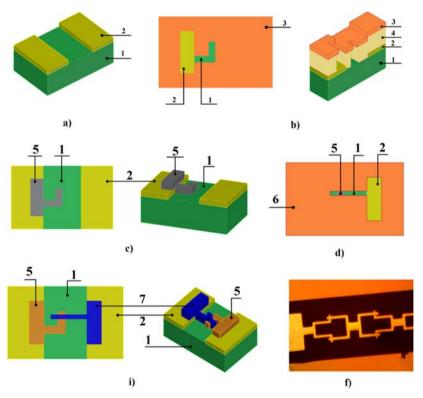

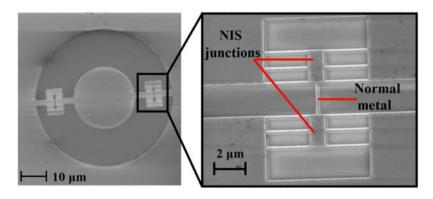

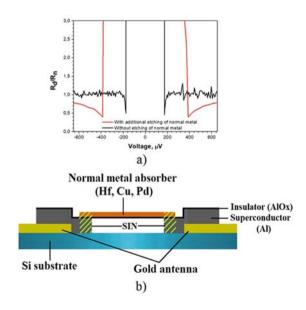

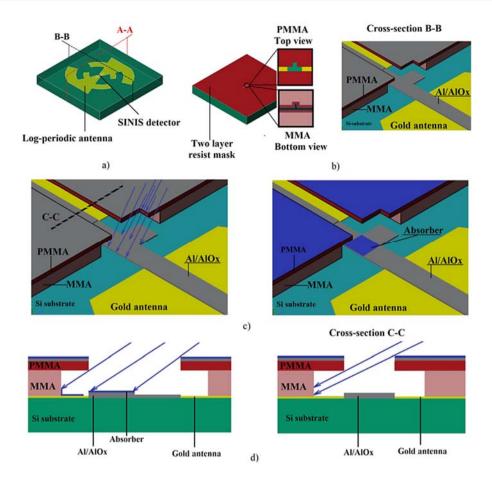

| 7.6. Fabrication Technique of SINIS Detectors with a Suspended Absorber by a Direct Write Lithography |     |

| 7.7. Fabrication Technique of SINIS Detectors with Suspended Absorber by a Shadow                     | 200 |

| Evaporation of Normal Metal                                                                           | 202 |

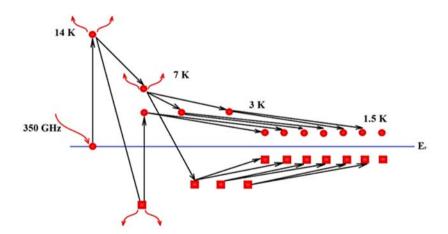

| 7.8. Evolution of the Theory and Characteristics of the SINIS Detector                                | 202 |

| with the Development of Its Fabrication Technology                                                    | 202 |

| 7.9. Conclusions.                                                                                     |     |

| Acknowledgements                                                                                      |     |

| References                                                                                            |     |

|                                                                                                       | 212 |

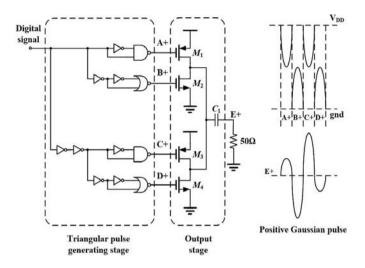

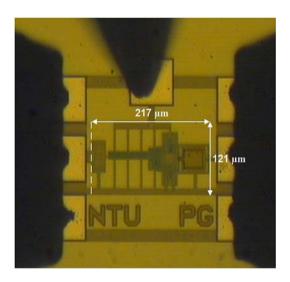

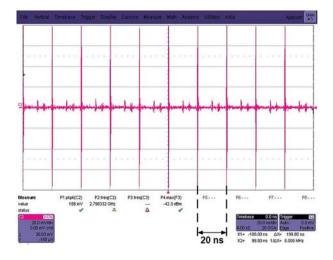

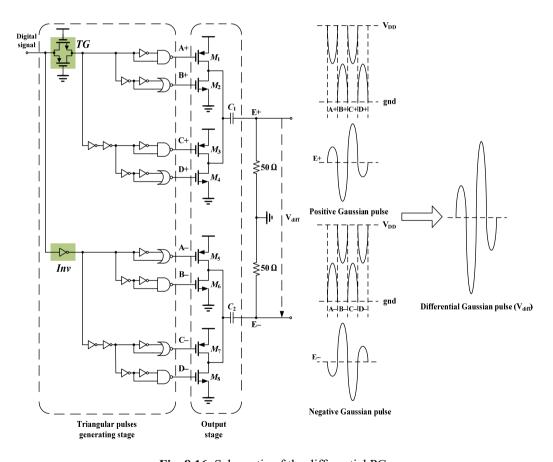

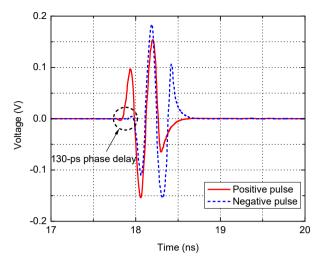

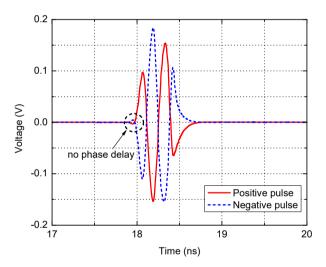

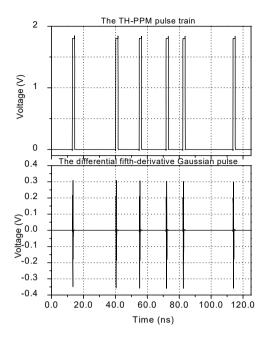

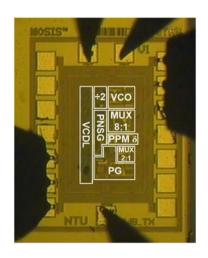

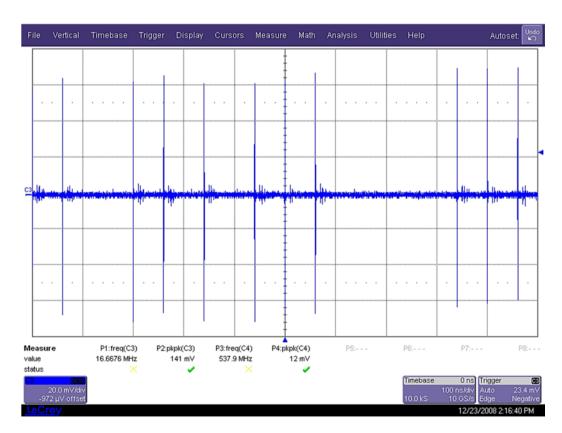

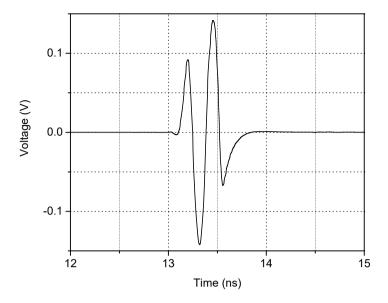

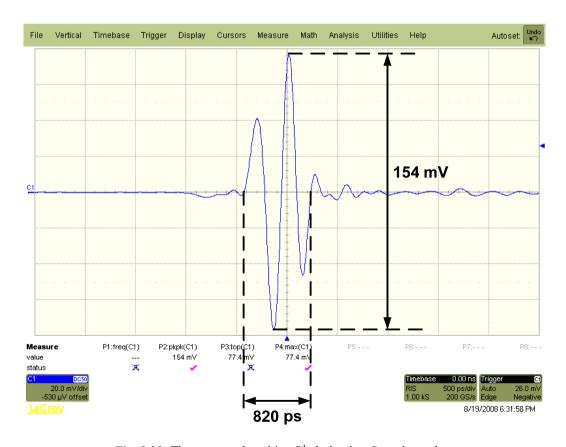

| 8. CMOS UWB Differential Impulse Radio Transmitter                                                    | 213 |

| 8.1. CMOS UWB Fifth-derivative Gaussian Pulse Generator                                               |     |

| 8.1.1. Introduction                                                                                   |     |

| 8.1.2. The Fifth-derivative Gaussian Pulse Generator                                                  |     |

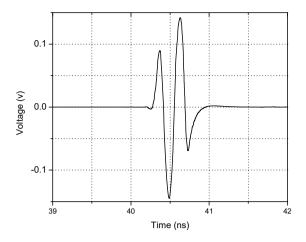

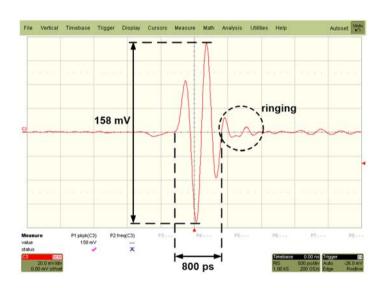

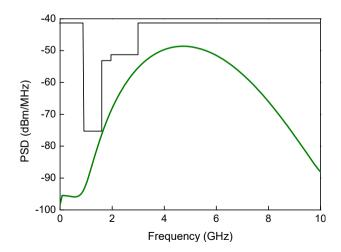

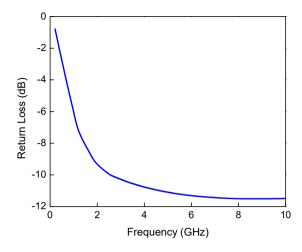

| 8.1.3. Measurement Results and Discussions                                                            |     |

| 8.1.4. Conclusion                                                                                     | 219 |

| 8.2. CMOS UWB Differential Impulse Radio Transmitter                                                  | 219 |

| 8.2.1. Introduction                                                                                   |     |

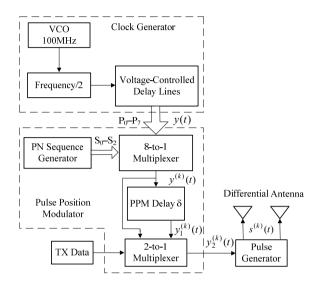

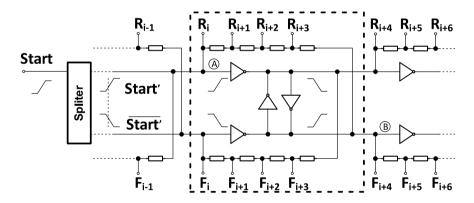

| 8.2.2. Impulse Radio Transmitter Architecture                                                         | 220 |

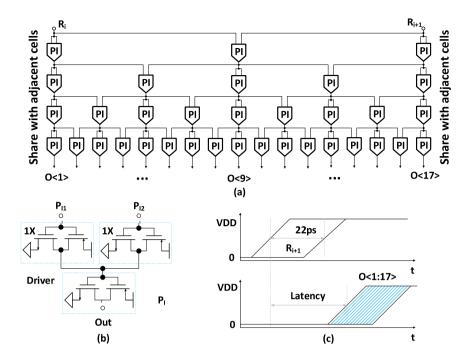

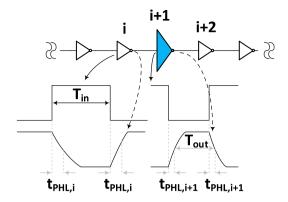

| 8.2.3. Impulse Radio Transmitter Circuits                                                             |     |

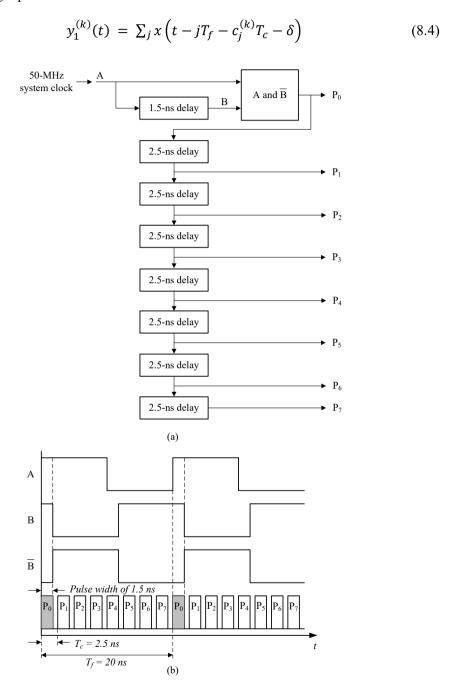

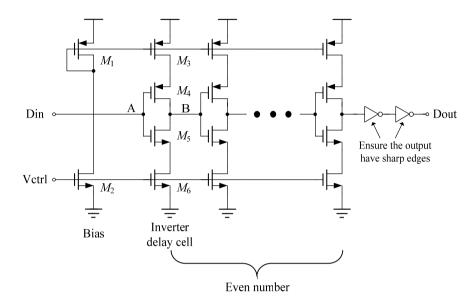

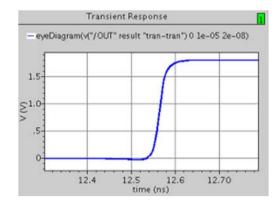

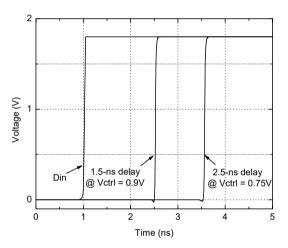

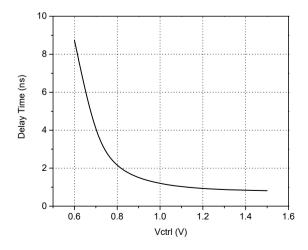

| 8.2.3.1. Voltage-controlled Delay Lines                                                               | 223 |

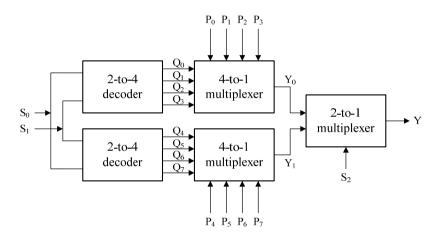

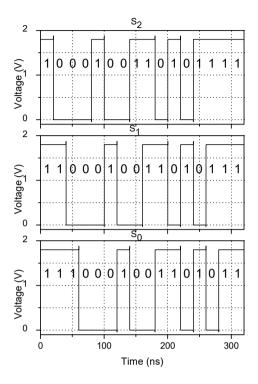

| 8.2.3.2. 8-to-1 Multiplexer and PPM Delay Cell                                                        |     |

| 8.2.3.3. Pseudorandom Number Sequence Generator                                                       |     |

| 8.2.3.4. Pulse Generator                                                                              |     |

| 8.2.4. Measurement Results and Discussions                                                            |     |

| 8.2.5. Conclusion                                                                                     |     |

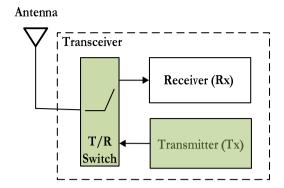

| 8.3. CMOS UWB Switches for Impulse Radio Transceiver                                                  |     |

| 8.3.1. Introduction                                                                                   | 234 |

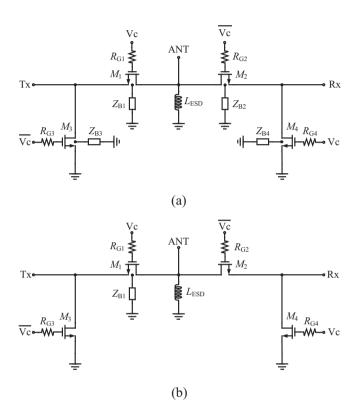

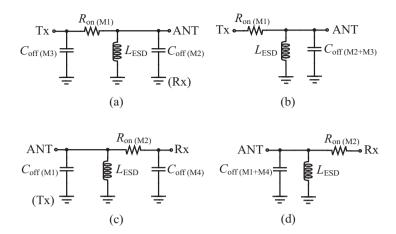

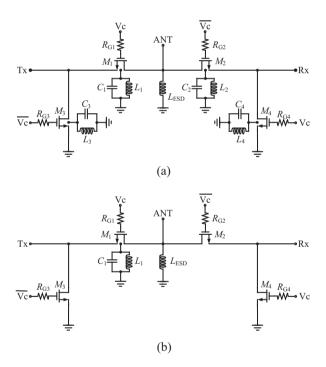

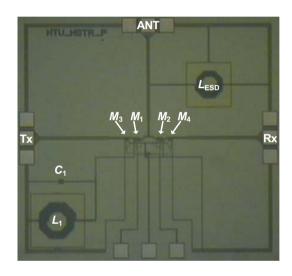

| 8.3.2. Asymmetric Topology for CMOS T/R Switch                                                        |     |

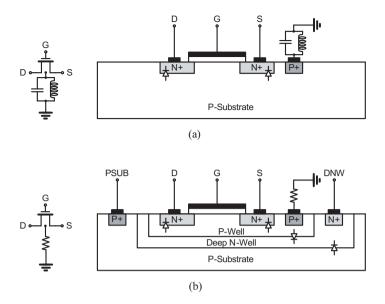

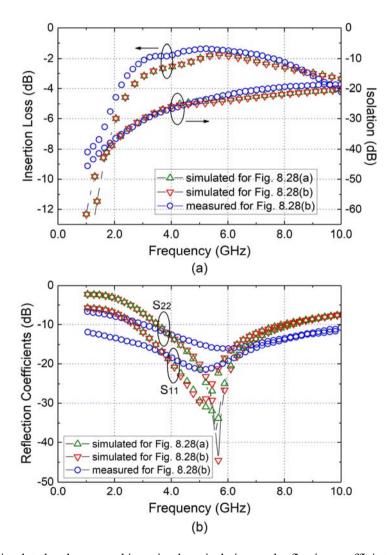

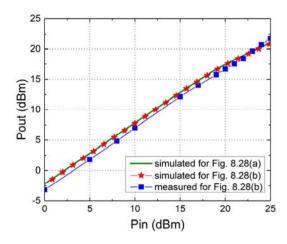

| 8.3.3. Evaluation of the Body-floating Techniques                                                     |     |

| 8.3.3.1. The LC-tuned Body-floating Technique                                                         |     |

| 8.3.3.2. The Resistive Body-floating Technique                                                        |     |

| 8.3.3. Performance Comparison and Discussion                                                          | 245 |

| 8.3.4. Conclusion                                                                         | 245 |

|-------------------------------------------------------------------------------------------|-----|

| Acknowledgments                                                                           | 246 |

| References                                                                                |     |

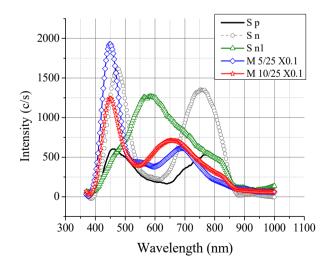

| 9. Printed Layers of ZnO-based Diluted Magnetic Semiconductors:  Fabrication and Research | 251 |

| 9.1. Introduction                                                                         | 251 |

| 9.2. Method for Sample Manufacturing                                                      |     |

| 9.3. Objectives of Researches.                                                            |     |

| 9.4. Methods for Layer Characterization                                                   |     |

| 9.5. Structural, Optical and Magnetic Properties of Printed ZnO:Co Layers                 |     |

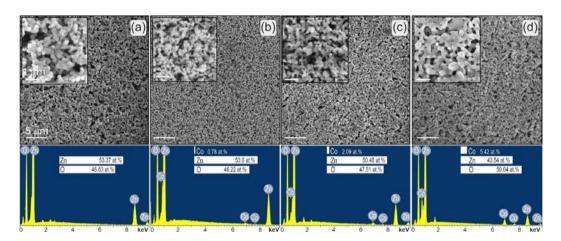

| 9.5.1. Morphology and Composition Analysis                                                |     |

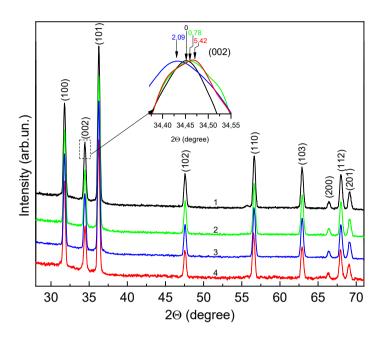

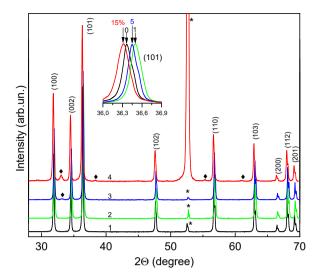

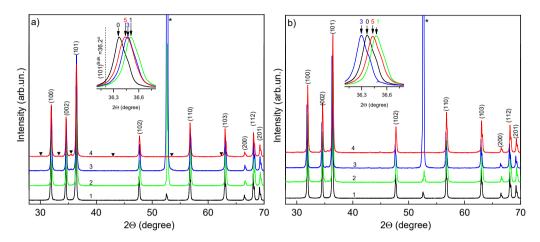

| 9.5.2. X-ray Diffraction (XRD) Analysis                                                   |     |

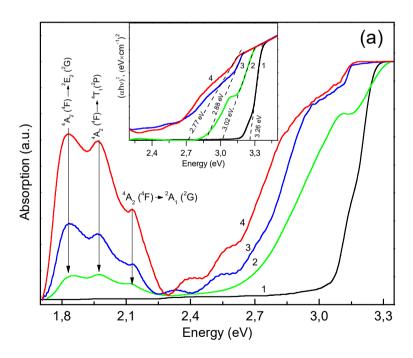

| 9.5.3. Optical Absorption Spectra                                                         |     |

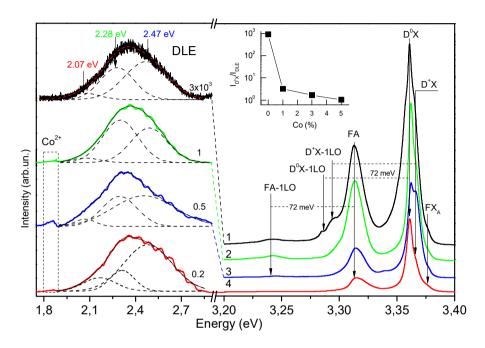

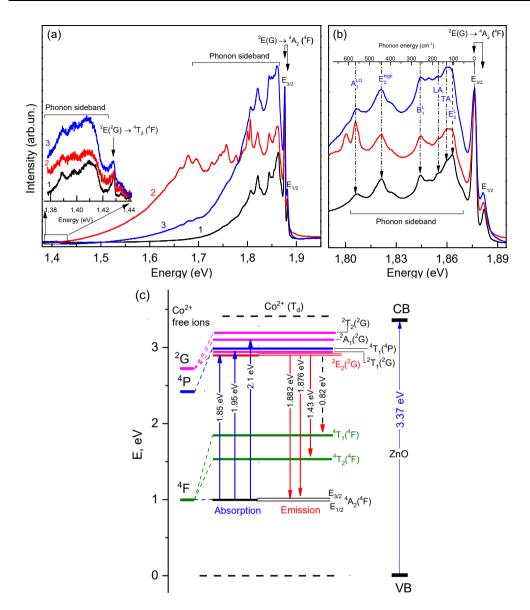

| 9.5.4. Photoluminescence                                                                  |     |

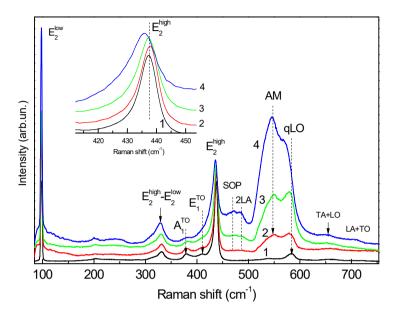

| 9.5.5. Raman Scattering                                                                   | 263 |

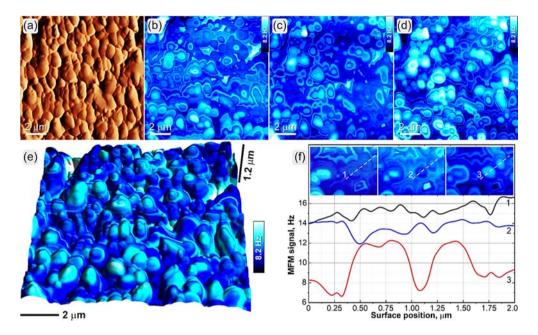

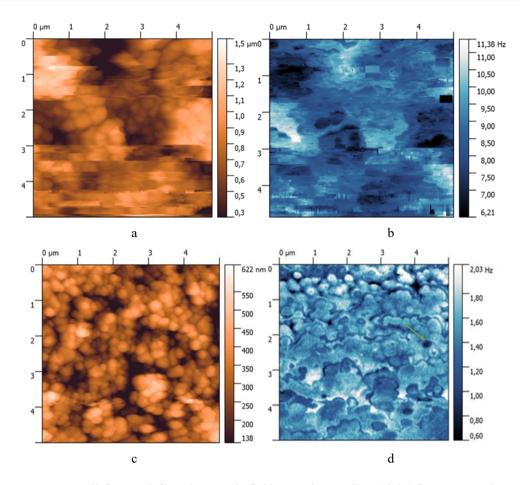

| 9.5.6. Atom Force Microscopy and Magnetic Force Microscopy                                |     |

| 9.6. Structural, Optical and Magnetic Properties of Printed ZnO:Mn Layers                 |     |

| 9.6.1. Morphology and Composition Analysis                                                |     |

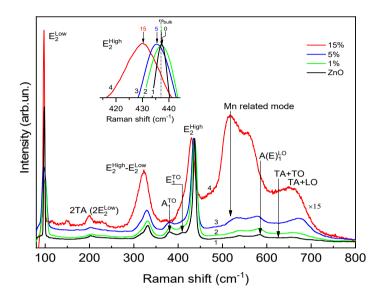

| 9.6.2. Raman Scattering                                                                   |     |

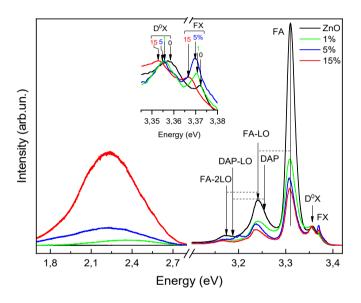

| 9.6.3. Photoluminescence                                                                  |     |

|                                                                                           |     |

| 9.7. Structural, Optical and Magnetic Properties of Printed ZnO:Fe Layers                 | 272 |

| 9.7.1. Morphology and Composition Analysis                                                |     |

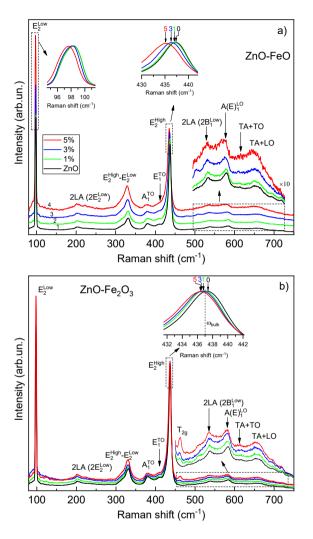

| 9.7.2. Micro-Raman Studies                                                                |     |

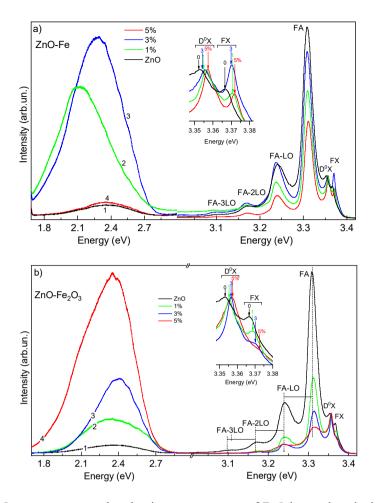

| 9.7.3. Photoluminescence                                                                  |     |

| 9.7.4. Magnetic Properties of Fe-doped ZnO Layers                                         | 2/6 |

| 9.8. Conclusions                                                                          |     |

| Acknowledgements                                                                          | 280 |

| References                                                                                | 280 |

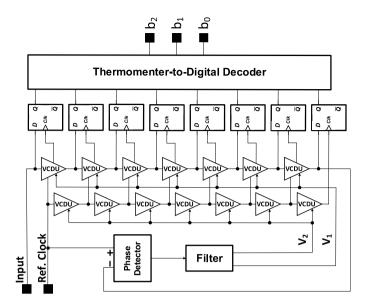

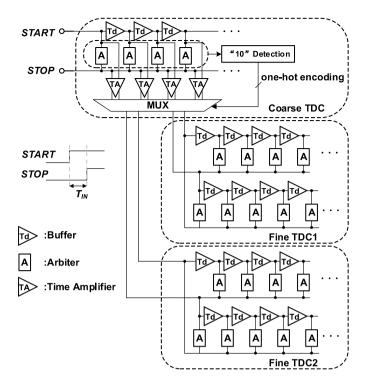

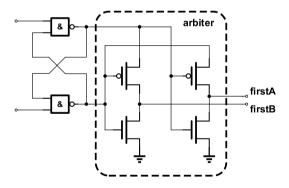

| 10. Time-to-digital Converters                                                            | 287 |

| Introduction                                                                              |     |

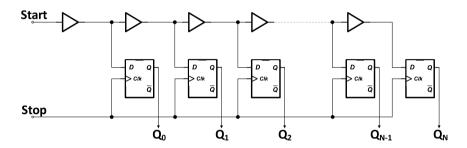

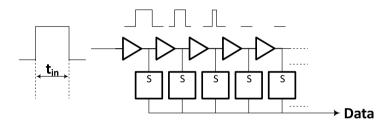

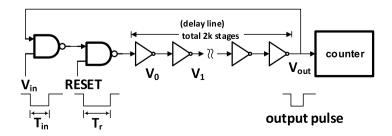

| 10.1. Flash TDC                                                                           |     |

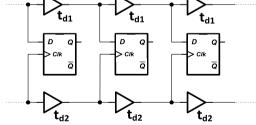

| 10.1.1 Delay Line TDC                                                                     |     |

| 10.1.1. Detay Line TDC                                                                    |     |

|                                                                                           |     |

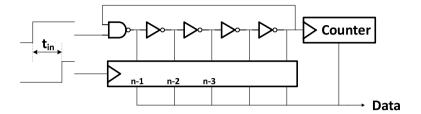

| 10.2. Vernier TDC                                                                         |     |

| 10.2.1. Vernier Delay Line TDC                                                            |     |

| 10.2.2. Vernier Ring Delay Line TDC                                                       |     |

|                                                                                           |     |

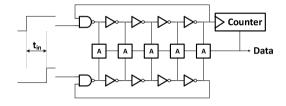

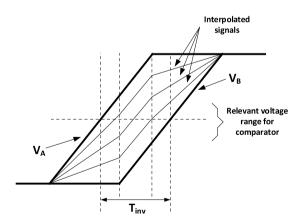

| 10.3. Interpolation TDC                                                                   |     |

| 10.3.1. Passive Interpolation TDC                                                         |     |

| 10.3.2. Active Interpolation TDC                                                          |     |

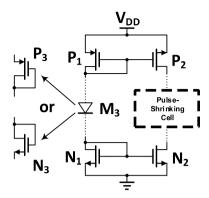

| 10.4. Pulse-shrinking TDC                                                                 |     |

| 10.5. Pipeline TDC                                                                        | 295 |

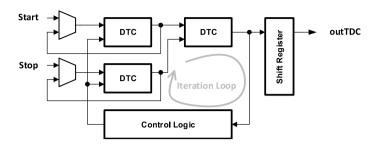

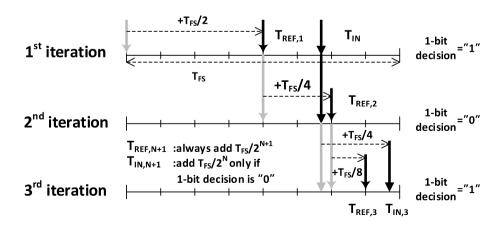

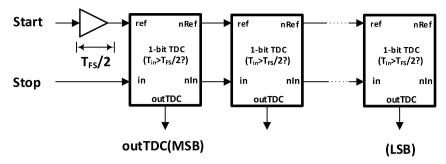

| 10.6. Successive Approximation TDC                                                        | 295 |

| 10.6.1. Typical SAR TDC                                                                   |     |

| 10.6.2. Decision-select Structure                                                         |     |

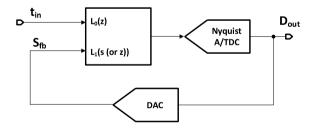

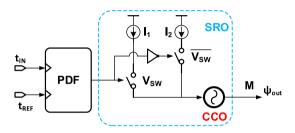

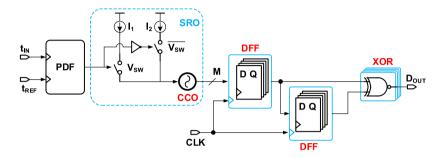

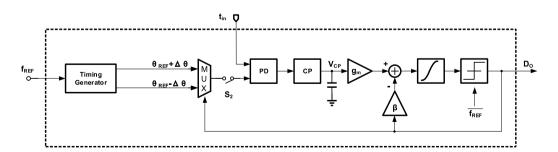

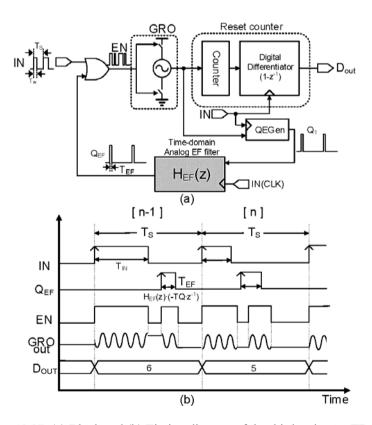

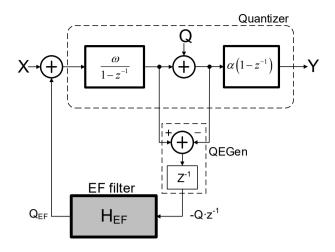

| 10.7. ΔΣ TDC                               | 298 |

|--------------------------------------------|-----|

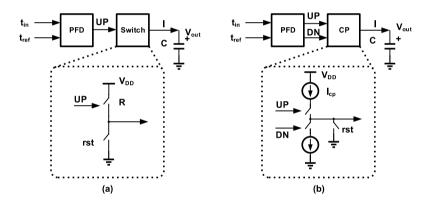

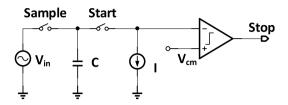

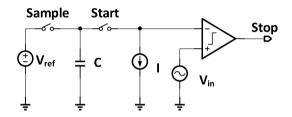

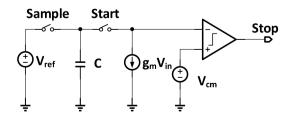

| 10.7.1. Time-to-voltage Integrator         | 299 |

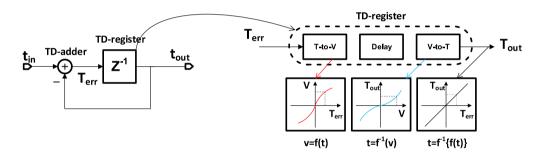

| 10.7.2. Time-domain Integrator             | 300 |

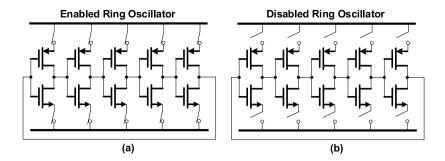

| 10.7.3. Phase-domain Integrator            |     |

| 10.7.4. Voltage-to-time Converter          |     |

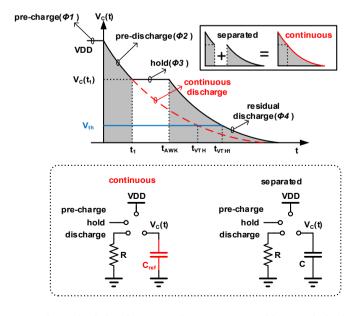

| 10.7.4.1. One-time Method                  | 302 |

| 10.7.4.2. Cyclical Method                  |     |

| 10.7.5. First-order $\Delta\Sigma$ TDC     |     |

| 10.7.5.1. Time-to-voltage Integrator Based | 306 |

| 10.7.5.2. Time-domain Integrator Based     |     |

| 10.7.5.3. Phase-domain Integrator Based    |     |

| 10.7.6. High Order $\Delta\Sigma$ TDC      |     |

| 10.8. Conclusions.                         | 311 |

| References                                 | 312 |

| Index                                      | 315 |

# **Contributors**

### M. Aceves-Mijares

Electronics department, National Institute of Astrophysics, Optics and Electronics (INAOE), P.O. Box 51, 72000, Puebla, México

### J. Alarcon-Salazar

Hollingsworth & Vose Co., R&D Scientist, Apizaco, Tlaxcala, México CP 90308, México

### Roberto Baca-Arroyo

Department of Electronics, School of Mechanical and Electrical Engineering, National Polytechnic Institute, 07738 Mexico City, Mexico,

E-mail: rbaca02006@yahoo.com.mx

### Rawid Banchuin

Graduated school of IT and Faculty of Engineering, Siam University, Bangkok, Thailand

## **Hajdin Ceric**

Institute for Microelectronics, TU Wien, 1040 Wien, Austria

### Tso-Fu Mark Chang

Institute of Innovative Research, Tokyo Institute of Technology, 4259 Nagatsuta-cho, Midori-ku, Yokohama, 226-8503, Japan

### A. M. Chekushkin

Institute of Radio Engineering and Electronics V. A. Kotelnikov RAS, Moscow, Russia

### Chun-Yi Chen

Institute of Innovative Research, Tokyo Institute of Technology, 4259 Nagatsuta-cho, Midori-ku, Yokohama, 226-8503, Japan

### C. Domínguez

Institut de Microelectrónica de Barcelona (IMB-CNM, CSIC), Universitat Autònoma de Barcelona, 08193 Bellaterra, Spain

### M. Yu. Fominskii

Institute of Radio Engineering and Electronics V. A. Kotelnikov RAS, Moscow, Russia

### A. A. González-Fernández

Institut de Microelectrónica de Barcelona (IMB-CNM, CSIC), Universitat Autònoma de Barcelona, 08193 Bellaterra, Spain

Electronics department, National Institute of Astrophysics, Optics and Electronics (INAOE), P.O. Box 51, 72000, Puebla, México

### A. A. Gunbina

Institute of Applied Physics of the RAS, Nizhny Novgorod, Russia Institute of Radio Engineering and Electronics V. A. Kotelnikov RAS, Moscow,

E-mail: aleksandragunbina@mail.ru

### Jin He

School of Physics and Technology, Wuhan University, Wuhan 430072, China E-mail: jin.he@whu.edu.cn

### J. Hernández-Betanzos

Electronics department, National Institute of Astrophysics, Optics and Electronics (INAOE), P.O. Box 51, 72000, Puebla, México

### Hiroyuki Ito

Institute of Innovative Research, Tokyo Institute of Technology, 4259 Nagatsuta-cho, Midori-ku, Yokohama, 226-8503, Japan

### O. F. Kolomys

V. Lashkarev Institute of Semiconductor Physics, National Academy of Sciences of Ukraine, Kiev, Ukraine

### Toshifumi Konishi

NTT Advanced Technology Cooperation, 3-1 Morinosato Wakamiya, Atsugi, Kanagawa, 243-0124, Japan

### Roberto Lacerda de Orio

Institute for Microelectronics, TU Wien, 1040 Wien, Austria

### Shuo Li

School of Physics and Technology, Wuhan University, Wuhan 430072, China

### X. Luna

Electronics department, National Institute of Astrophysics, Optics and Electronics (INAOE), P.O. Box 51, 72000, Puebla, México

### P. M. Lytvyn

V. Lashkarev Institute of Semiconductor Physics, National Academy of Sciences of Ukraine, Kiev, Ukraine

### Katsuyuki Machida

Institute of Innovative Research, Tokyo Institute of Technology, 4259 Nagatsuta-cho, Midori-ku, Yokohama, 226-8503, Japan

### Kazuya Masu

Institute of Innovative Research, Tokyo Institute of Technology, 4259 Nagatsuta-cho, Midori-ku, Yokohama, 226-8503, Japan

### Niansong Mei

Shanghai Advanced Research Institute, Chinese Academy of Sciences Shanghai, 201210, China

### Michal Micjan

Slovak University of Technology in Bratislava, Ilkovicova 3, 81219 Bratislava, Slovakia

### D. V. Nagirnaya

Institute of Radio Engineering and Electronics V. A. Kotelnikov RAS, Moscow, Russia

### Hideaki Nakajima

Institute of Innovative Research, Tokyo Institute of Technology, 4259 Nagatsuta-cho, Midori-ku, Yokohama, 226-8503, Japan

### J. Pedraza

Electronics department, National Institute of Astrophysics, Optics and Electronics (INAOE), P.O. Box 51, 72000, Puebla, México

### G. S. Pekar

V. Lashkarev Institute of Semiconductor Physics, National Academy of Sciences of Ukraine, Kiev, Ukraine

### Siegfried Selberherr

Institute for Microelectronics, TU Wien, 1040 Wien, Austria

### A. F. Singaevsky

V. Lashkarev Institute of Semiconductor Physics, National Academy of Sciences of Ukraine, Kiev, Ukraine

### Masato Sone

Institute of Innovative Research, Tokyo Institute of Technology, 4259 Nagatsuta-cho, Midori-ku, Yokohama, 226-8503, Japan

### V. V. Strelchuk

V. Lashkarev Institute of Semiconductor Physics, National Academy of Sciences of Ukraine, Kiev, Ukraine

### M. A. Tarasov

Institute of Radio Engineering and Electronics V. A. Kotelnikov RAS, Moscow, Russia

### Hiroshi Toshiyoshi

Institute of Industrial Science, The University of Tokyo, 4-6-1, Komaba, Meguro-ku, Tokyo, 153-8904, Japan

### **Martin Weis**

Slovak Univerrsity of Technology in Bratislava, Ilkovicova 3, 81219 Bratislava, Slovakia

### **Daisuke Yamane**

Department of Mechanical Engineering, Ritsumeikan University, 1-1-1 Noji-Higashi, Kusatsu, Shiga 525-8577, Japan

### **Puqing Yang**

Shanghai Advanced Research Institute, Chinese Academy of Sciences Shanghai, 201210, China

### R. A. Yusupov

Institute of Radio Engineering and Electronics V. A. Kotelnikov RAS, Moscow, Russia

### Houman Zahedmanesh

Institute for Microelectronics, TU Wien, 1040 Wien, Austria

# **Preface**

The 3<sup>rd</sup> volume continues the popular open access Book Series on 'Advances in Microelectronics: Reviews'. But as usually, it is not a simple set of reviews. Each chapter contains the extended state-of-the-art followed by new, unpublished before, obtained research results. The 1<sup>st</sup> and 2<sup>nd</sup> volumes from this Book Series have been published in 2017 and 2019 years accordingly.

Written by 40 contributors from academy and industry from 9 countries (Austria, China, Japan, Mexico, Russia, Slovak Republic, Spain, Thailand and Ukraine) the book contains 10 chapters from different areas of microelectronics: MEMS, semiconductors and various microelectronic devices.

Chapter 1 is devoted to organic electronics materials, devices, and applications. First, the charge transport phenomenon in organic materials is explained, and methods for charge transport evaluation are briefly described. Afterwards, organic electronic devices such as organic field-effect transistors, organic light-emitting devices, and organic solar cells are introduced and explained.

Chapter 2 describes one alternative to mitigate the electronic waste issue next years, where reconfigurable conduction mode in semiconductor devices is suggested to demonstrate how emergent functional devices might be driven by using scalable circuit technologies encouraged on recyclability actions into the electronics' industry.

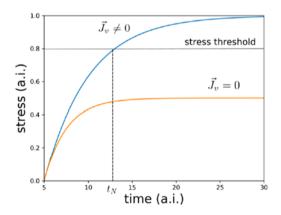

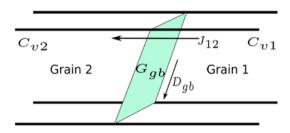

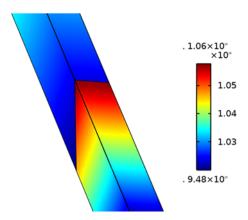

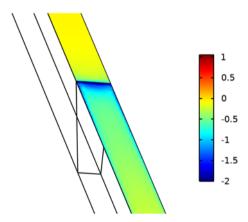

Chapter 3 presents a comprehensive approach to modeling and simulation of degradation phenomena affecting the reliability of modern nano-scaled interconnects. The dependence of interconnect lifetimes on length, thickness, and the diffusivities of the cap layers obtained by simulation are discussed in relation to experimental results.

Chapter 4 discuss the analytical models of process induced random variation of FGMOSFET. In the technological aspect, some of these models are dedicated to the above 100 nm FGMOSFET where the others are oriented to the nanometer FGMOSFET. Mathematically, some of them are statistical models where the rests are probabilistic ones.

Chapter 5 describes the Effective Young's modulus of electrodeposited gold for design of movable components in MEMS devices. The evaluation is conducted by a non-destructive resonance frequency method. Specimens used in the evaluation are pure gold microcantilevers prepared by electrodeposition and lithography. An increase in the effective Young's modulus is observed as the width of the micro-cantilever varied from 10 to 25 micrometer.

Chapter 6 is devoted to electrophotonic seamless circuits. This includes their basic components, namely the light source, the waveguide and the photodetector, all in silicon. Especial emphasis is placed on a novel integrable silicon photosensor, presenting the

physics and mathematics involved in it. Computational simulations corroborating the developed model are presented.

Chapter 7 describes different technologies for fabrication of nanodevices with aluminium superconducting tunnel junctions. The main building block of our devices is superconductor-insulator-normal metal-insulator-superconductor (SINIS) structure - one of the promising types of subTHz detectors. The progresses in theoretical modeling, experimental studies, and fabrication technologies is presented. Such technologies were also used for fabrication of aluminium SIS junctions and SQUID amplifiers.

Chapter 8 discusses a fully integrated differential impulse radio transmitter for ultrawideband (UWB) applications. The fifth-derivative Gaussian pulse generator is implemented using a 0.18- $\mu$ m CMOS process with low power consumption and low circuit complexity.

Chapter 9 describes the revealed ferromagnetic properties in diluted magnetic semiconductors which were Co-, Mn- and Fe-doped ZnO layers prepared by printing. The magnetization was found to be maximal in ZnO: $Fe_3+$  layers, about two times higher than in ZnO layers doped with  $Co_2+$ ,  $Mn_2+$  and  $Fe_2+$  ions. On the basis of comprehensive studies of layers by various methods, the physical nature of the most important properties of the layers was established.

Chapter 10 contains the review of the Time-to-Digital Converters (TDC) state-of-the-art technology. The aim of the chapter is to help readers understand the principle and development trend of TDC. The concepts and investigations presented in this book chapter mainly originate from research results of peers all over the world.

I shall gratefully receive any notices, comments and suggestions from readers to make the next volume of 'Advances in Microelectronics: Reviews' interesting and useful.

Dr. Sergey Y. Yurish Editor

IFSA Publishing

Barcelona, Spain

# **Chapter 1**

# **Organic Electronic Materials and Devices**

# Michal Micjan and Martin Weis

### 1.1. Introduction

Human society made great progress in the last century because of science and technology. Various fields of technology improved the quality of human life, and one of the key roles had the dawn of electronics. As a leading representative of semiconducting materials, silicon is the inherent part of all electronic devices today and represents state-of-the-art electronics.

On the other hand, material science and research in the field of electronics are focused on alternative materials such as organic semiconductors. An organic semiconductor is a broad family of organic molecular materials that exhibit specific properties similar to inorganic semiconductors. Interestingly, molecular materials show only weak forces between the molecules, giving new deposition methods. The low-temperature evaporation in a vacuum is applicable for various small molecules, whereas "wet technologies" using organic material solubility in solvents are popular for large molecules and polymers. The thin-film fabrication technology is not a unique property of these materials; organic semiconductors exhibit semiconducting properties even without any doping, and the doping process only suppresses semiconducting properties. Hence, the organic semiconductors do not represent only alternative semiconducting materials, but it is also an exciting challenge for electronics and device physics.

The very first success in the field of organic electronics was metal-insulator-semiconductor (MIS) diode using polyacetylene and polysiloxane as organic semiconductor and insulator, respectively [1]. This pioneering work in 1983 demonstrated the possibility of organic material application in electronics. Three years later, researchers Tsumura, Koezuka and Ando from Mitsubishi Chemical company published fabrication of organic field-effect transistor (OFET) based on polythiophene as organic semiconductor [2]. However, the effective mobility of free charge carriers reached a level of only  $10^{-5}$  cm<sup>2</sup>/V.s, it was an exceptional success that opened a new field and inspired

Martin Weis

many research labs. The report on the first organic solar cell had been published by Tang in 1986 [3], and one year later, the first organic light-emitting diode (OLED) had been reported by Tang a Van Slyke [4]. It is interesting to note that Eastman Kodak's private company has fabricated both the first organic solar cells and OLED devices. These excellent achievements stand for the beginning of the new age in electronics, applying organic materials for electronic devices. In contrast to inorganic semiconducting materials, organic molecular materials have many variabilities in structure, an almost unlimited number of derivatives can be synthesised. Hence, after first success with well-known organic materials, organic chemistry and material science focused on designing novel materials with improved electrical properties. The first devices used insoluble polymers cross-linked directly on the substrate; however, the "holy grail" of the industry was soluble semiconducting materials [5] that can be deposited using printing technologies such as inkjet printer or various roll-to-roll depositions. Since the solution-based technologies may strongly reduce the fabrication costs, the low-cost deposition was a driving force for the applied research. Although organic semiconductors have been envisioned as potential candidates for future electronics, many research labs had doubts about the market's impact, and the research progress was only very slow. Therefore, we can state that the next milestone was Gilles Horowitz's work [6], which used the common approach used in the field of semiconductor physics to explain OFETs. It must be emphasised that this work did not use any new concept, and certain parts are even incorrect since they are based on the assumptions on material doping. Nevertheless, this work inspired many researchers to extend their study on organic materials and also, the private companies made large investments in the applied research. Furthermore, in the '70s has been established the second important class of organic materials, conjugated polymers, also denoted as synthetic metals. The successful synthesis and controlled doping of conjugated polymers by Alan G. MacDiarmid, Alan J. Heeger, and Hideki Shirakawa were honoured with the Nobel Prize in Chemistry in the year 2000.

During the next two decades, the research papers demonstrated novel organic materials' capabilities, suggested new device designs and deposition technologies. As a result, organic electronics have been established as a new interdisciplinary field comprising material science, organic chemistry, physics, and electronics. The fundamental research was a strong basis for applications. OLED devices have been fabricated in the matrix; thus, the OLED displays were introduced as a competitor of liquid crystals displays (LCD). The OSC already reached an efficiency better than 13% [7], which is more than comparable with amorphous silicon or polycrystalline silicon solar cells. The new field already had certain success on the market. OLED displays are used not only for television sets but also for mobile devices because of low power consumption and great performance. Also, the OLED lighting recently found its opportunity on the market and start to have commercial success.

The broad range of organic electronics applications encourages researchers for novel approaches in material design, characterisation methods, or fabrication technology. Organic electronics technology promises low-cost devices and other advantages such as transparency, flexibility, etc. Hence, we can expect that application will hit the market mostly in the following areas:

- OLED displays and lighting: OLED displays already reached higher quality and lower price than LCDs. Cheap and energy-efficient OLED lighting with a very natural spectrum is a plausible alternative to inorganic LED lighting. In addition, the flexibility offers mechanical resistance;

- Photovoltaics: low-cost materials are already now the suitable replacement of inorganic solar cells used for daily applications;

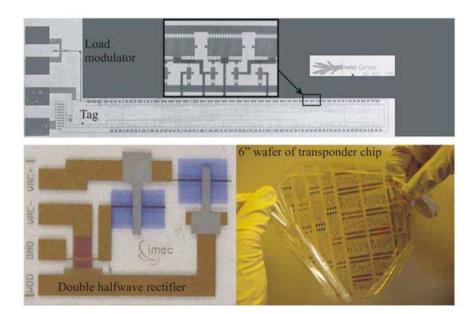

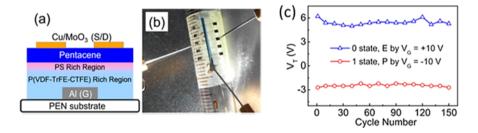

- Memories and logic circuits: low-cost fabrication and flexibility are key points for smart packaging (especially RFID tags) and the internet of things (IoT) devices;

- Medical electronics and sensors: the growing interest in monitoring an individual's health state has raised a need for flexible sensors, wearable electronics, and smart systems that organic electronics devices can provide.

Although all envisioned ideas make organic electronics a promising candidate for future electronic devices, complex circuits based on organic transistors are still under development and did not reach the level required by industry. The research progress based on material science is similar to OLED or organic solar cell devices; however, a deep understanding of charge transport phenomena is needed to achieve greater electrical properties. It has been found that the semiconducting properties have a different microscopic origin than the inorganic materials, even though the macroscopic behaviour is sometimes almost identical. Interestingly, in contrast with his previous ideas, also Gilles Horowitz comments that "organic semiconductors" can be a misleading term and suggests calling these materials "organic semi-insulators", but it is too late for such a correction [8]. Organic semiconductors belong to the broad family of dielectric materials, and their properties range from insulating up to semiconducting.

This book chapter makes a brief introduction to organic electronics materials and devices. First, the charge transport phenomenon in organic materials is explained, and methods for charge transport evaluation are briefly described. Afterwards, the organic electronic devices are introduced and explained: (i) Organic field-effect transistors; (ii) Organic light-emitting devices, and (iii) Organic solar cells.

# 1.2. Charge Transport Phenomenon in Organic Semiconductors

Organic semiconductors are carbon-based materials that exhibit specific electronic properties of their inorganic counterparts; however, there is a huge discrepancy between them in the structure that rules the charge transport's undelaying physics. The inorganic semiconductors are consist of specific atoms ordered in atomic crystal with mutual covalent bonds. In the case of organic semiconductors, the atoms are covalently bonded only inside of the molecule, whereas the molecules have van der Waals intermolecular bonding, and they are ordered in molecular crystal. As a result, the more significant separation between the molecules does not provide the mechanical flexibility, solubility in organic solvents; however, it also leads to the weaker delocalisation of electron wavefunction that affects the charge transport. Furthermore, in the case of organic

materials, we always meet significantly lower order. The small molecules are primarily polycrystalline, and long-chain polymer materials have mostly amorphous structure.

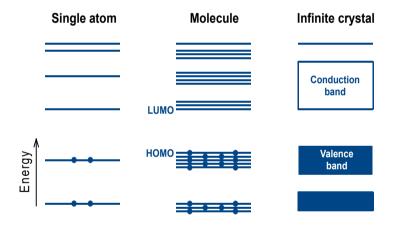

The molecular structure of organic semiconductors with a small number of atoms leads to the unique energy band structure in contrast with "infinite" crystalline solids. While the electrons of a single atom are allowed to occupy several well-defined energy levels, the interaction of multiple atoms leads to the energy level splitting to avoid degenerated (multi-state) level. Solid-state physics teaches us that infinite crystals are the cause of the fine structure denoted as an energy band, as illustrated in Fig. 1.1. In inorganic semiconductors, the highest-filled energy band called the valence band, and the lowest unoccupied energy band is marked as the conduction band. The upper edge of the valence band and the lower edge of the conduction band are separated by the energy gap where no states are allowed. The limited number of atoms in a single molecule leads to separated energy levels, where each atomic orbital splits into several discrete molecular orbitals. Similar to the infinite crystals, we define the highest occupied molecular orbital (HOMO) and lowest unoccupied molecular orbital (LUMO) energy levels, Fig. 1.1. Again, the HOMO and LUMO energy levels are separated by the energy gap of forbidden states.

Fig. 1.1. Simplified energy band structure of a single atom, the molecule, and the infinite crystal.

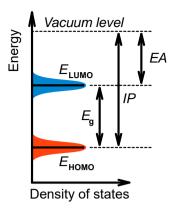

Even though the isolated single molecule has a well-defined energy level structure, the mutual interaction between molecules cannot be neglected in molecular solids. Due to lack of order, the molecular solids are polycrystalline or even amorphous. The disorder induces the broadening of the energy levels [9-11], and the density of states (DoS) can be often approximated by a Gaussian distribution, see Fig. 1.2.

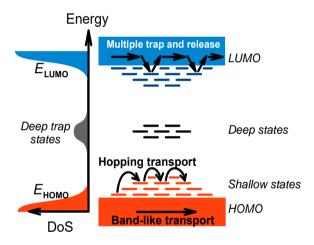

The degree of order in molecular solids rules the charge carrier transport mechanism in organic semiconductors. Hence, we can distinguish the most common levels of order as follows: (i) crystalline, (ii) crystalline with defects (*e.g.* polycrystalline), and (iii) amorphous. The crystalline molecular solids show the band-like transport [12-14]. Already a minor disorder causes the distribution of states, see Fig. 1.3, which creates shallow states close to the HOMO (or LUMO) level.

**Fig. 1.2.** The energy levels in organic semiconductor solids. Energy levels HOMO and LUMO are broadened due to intermolecular interaction. The ionisation potential (IP) is the energy required to remove one electron from the HOMO level, while the electron affinity (EA) stands for the energy of adding one electron from the vacuum level to the LUMO level.

**Fig. 1.3.** The density of states and schematic spatial and energy diagram of organic semiconductor with trap states in the energy gap.

Consequently, the charge trapping takes place, and multiple trap-and-release model can describe the charge transport [15-17]. In the highly disordered molecular systems, the charge transport happens due to the hopping between localised states [18-21].

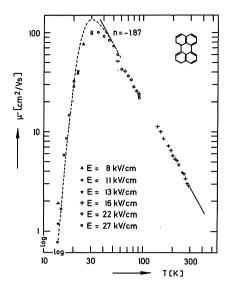

Let's have a deeper insight into the charge transport mechanisms. Ideal crystals have always been envisioned as the most critical requirement for scattering-free charge transport. Interestingly, already in the '80s, researchers succeed in the growth of single crystals of naphthalene and perylene [22-24]. The electron and hole mobilities obtained by the time-of-flight method reached a level as high as 400 cm<sup>2</sup>/V.s in the low-temperature region where the scattering due to thermal lattice vibration is suppressed, Fig. 1.4.

**Fig. 1.4.** Increase of the electron mobility in high purity single-crystalline α-perylene. In the log  $\mu$  vs. log T, plot straight lines indicate an inverse power law temperature dependence,  $\mu \propto T^{-n}$ , indicative of band transport with acoustic phonon scattering. At the lowest temperatures, multiple shallow trapping limited transport is dominant. Reprinted with permission from N. Karl, K.-H. Kraft, J. Marktanner, M. Münch, F. Schatz, R. Stehle, H.-M. Uhde, Journal of Vacuum Science and Technology A, Vol. 17, 1999, 2318. Copyright 1999, American Vacuum Society.

Such great value cannot be obtained in the presence of charge trapping or hopping transport. Note that the increase in carrier mobility with decreasing temperature follows power-law temperature dependence,  $\mu \propto T^{-n}$ , with the power of about 3/2, indicating the band transport with acoustic phonon scattering. Hence, single-crystal devices have been used to demonstrate the occurrence of band-like transport properties.

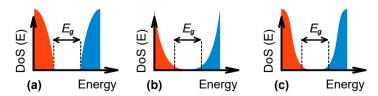

Before we start with the explanation of charge traps we need to move onto the DoS description. In an ideal crystal, the DoS at the band edge has delocalised (extended) states with a shape of a lying parabola,  $DoS \propto E^{1/2}$ , where E is the energy of the electronic state. Hence, the band edge is well defined and sharp. In the case of disordered semiconductors, the band edges cannot be precisely estimated. The band-tail states follow the Gaussian distribution or exponential distribution as depicted in Fig. 1.5.

**Fig. 1.5.** The density of states distribution energy of (a) ideal crystal semiconductor, or polycrystalline/amorphous organic semiconductor assuming, (b) exponential or (c) Gaussian distribution for band tail states.

The Gaussian disorder model has been introduced by Bässler [26] for organic materials as follows

$$DoS(E) = N_0 (2\pi\sigma^2)^{-1/2} \exp\left(-\frac{(E - E_{\text{HOMO}})^2}{2\sigma^2}\right),$$

(1.1)

where  $N_0$  is the number of states per uni volume, and  $\sigma$  stands for energy disorder, implying that all states are localised. On the other hand, Vissenberg and Matters [27] proposed exponential shape of DoS

$$DoS(E) = \frac{N_0}{kT_0} \exp\left(-\frac{E - E_{\text{HOMO}}}{kT_0}\right), \tag{1.2}$$

where k is the Boltzmann constant and  $T_0$  is the temperature parameter indicating the width of the exponential distribution. Even though there are many experimental results, there is no widely accepted model due to deviation from both approximations. Depending on the material, a single Gaussian, an exponential, or a combination of both functions is used [28-30].

It should be noted that the band tail electronic states localised within the bandgap serve as charge trapping states. In other words, trap states may have discrete levels and quasi-continuous energy distribution. As a result, the Gaussian or exponential band tails represent shallow trap states of an organic semiconductor. Trap states stand for the energetically favourable localised states; hence, the charge carrier detrapping time (reciprocal value of the attempt-to-escape frequency) can be even in the range of seconds. As a result, the effective value of the free charge carriers is drastically reduced. In the case of multiple shallow trapping with multiple thermal releases, the transport can be described by introducing a reduced average "effective mobility"  $\mu_{\rm eff}$ . Since this parameter includes reduced carrier density, it is a thermally activated material property.

Till now, we discussed the charge transport in single-crystal or polycrystalline organic semiconductors; however, amorphous organic semiconductors are a wide family of polymer-based materials that can be assumed as strongly disordered systems. Charge transport in such disordered organic semiconductors is carried out as hopping within a positionally random and energetically disordered system of localised states [30-32]. Even though the very pioneer work on hopping transport in organic solids was done by Bässler [26], the hopping transport in disordered semiconductors has been introduced by Mott in 1968 [33]. The variable range hopping transport has specific temperature dependence of the conductivity

$$\sigma(T) = \sigma_0 \exp\left(-\left(\frac{T_0}{T}\right)^{\alpha}\right),$$

(1.3)

where  $T_0$  is the characteristic temperature representing the effective energy barrier to hopping of charge carriers between localised states. The power exponent  $\alpha$  is equal to 1/(1+D), where D is the system's dimensionality. In other words, the power coefficient  $\alpha$  equal to 1/2 stands for 1D charge transport, while  $\alpha$  of 1/4 represents the charge hopping in all three dimensions [34-36].

The charge transport in organic semiconductors directly affects the electrical conductivity, the charge carrier concentration and mobility. Since there is no direct method to evaluate the mobility, it is assumed the effective mobility, which also includes the deviation of ideal carrier concentration. A number of methods have been proposed to estimate the effective value of mobility, such as:

- Time-of-flight (ToF) method;

- The space-charge-limited-current (SCLC) method;

- Charge carrier extraction by linearly increasing voltage (CELIV);

- The impedance spectroscopy method;

- The organic field-effect transistor (OFET) method.

Each approach has its own limitation, required approximations, and measurement conditions; hence, effective mobilities' obtained values are not fully comparable.

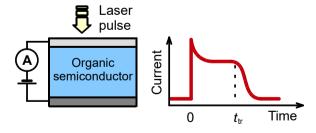

The time-of-flight (ToF) technique introduced by Kepler [37] uses a dielectric layer sandwiched between two electrodes where one of them is semi-transparent. If we use a short laser pulse to generate a charge carrier sheet near one electrode, the charge sheet will drift towards the other electrode due to the applied electric field. The transient current corresponds to the temporal change of the charge on the electrode generated by the approaching charge carrier sheet. As a result, the current starts to decay at the transit time  $t_{\rm tr}$ , when the charge carrier sheet arrives at the electrode, Fig. 1.6. Hence, the mobility  $\mu$  can be evaluated as

$$\mu = \frac{d^2}{V} \frac{1}{t_{\rm tr}},\tag{1.4}$$

where d is the dielectric film thickness, and V is the applied voltage. The film thickness is usually required to be more than 1  $\mu$ m to record the transit time. Note that a similar approach has also been used with electronic pulse applied on the OFET device [38-40], and it is often denoted as electronic time-of-flight (e-ToF).

Fig. 1.6. The time-of-flight setup and the ideal current measurement for non-dispersive transport.

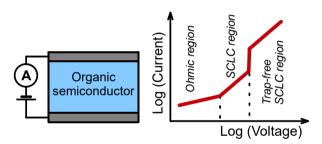

The space-charge limited current (SCLC) technique also uses the sandwich structure to extract the mobility from the steady-state current measurements [41]. If we assume a

single-carrier device (i.e. charge transport of only electron or only holes) with Ohmic contacts, the electric current density *J* follows the Mott-Gurney law

$$J = \frac{9}{8} \varepsilon \mu \frac{V^2}{d^3},\tag{1.5}$$

where  $\varepsilon$  is the dielectric constant of the dielectric layer. Even though the SCLC technique has been widely used for organic diodes, the mobility analysis is strongly influenced by the presence of traps [42, 43]. In details, in the low-voltage region, the current response is ohmic,  $J \propto V$ , whereas the higher voltage causes accumulation of the charge carriers in the dielectric film, and the further current injection is prohibited due to electric field compensation of the space-charge in the device. There the current follows the square of the voltage, where  $J \propto V^2$ ; however, mobility is still affected by the trapping. Once the voltage rises over trap-filled-limit voltage, the current abruptly rises,  $J \propto V^n$  where n=2, all the traps states are filled, the charge carriers flow through the device like in the trap-free material, and again the SCLC conditions are satisfied,  $J \propto V^2$ . Note that the log-log scale of current-voltage dependences is widely applied since the power dependences are linear, and the power exponent represents the slope of the current as depicted in Fig. 1.7.

Fig. 1.7. The SCLC setup and the current-voltage dependence in log-log scale.

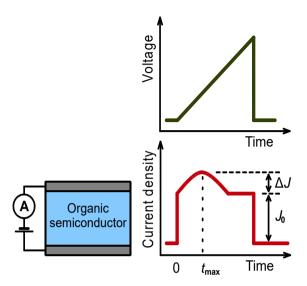

The charge carrier extraction by linearly increasing voltage (CELIV) is another technique applied for dielectric films sandwiched between electrodes. The main idea of CELIV is the extraction of the charge carriers present in the dielectric film by the applied external voltage. When the ramp voltage is applied with a slope of  $\beta = V/t_{\rm pulse}$ , the recorded current consists of the displacement current,  $J_0 = \varepsilon_0 \varepsilon_{\rm r} \beta/d$ , and the current due to extraction of the dominant charge carrier present in the device,  $\Delta J$  [44-46], see Fig. 1.8. The mobility can be evaluated using numerically estimated correction factors as

$$\mu = \frac{2d^2}{3At_{\text{max}}^2(1+0.36\Delta J/J_0)},\tag{1.6}$$

where  $t_{\rm max}$  corresponds to the time of maxima current density, see Fig. 1.8. The main limitation of the CELIV technique is that there is no possibility of distinguishing holes and electrons in ambipolar systems such as OLEDs or organic solar cells. It is also required a sufficiently high concentration of free charge carriers in the organic

semiconductor. In the case of low carrier concentration, continuous or a short light pulse illumination can be applied to photo-generate carriers, the so-called photo-CELIV technique.

**Fig. 1.8.** The CELIV setup and the temporal dependence of the voltage ramp and recorded current density.

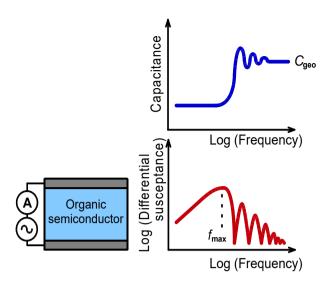

The impedance spectroscopy (or admittance spectroscopy) has also been proposed to evaluate organic electronics devices' charge transport properties. In details, the small-signal  $V_{\rm ac}$  is superposed on the voltage offset  $V_{\rm dc}$  to probe the frequency-dependent response. The determination of mobility using impedance spectroscopy is based on a single-carrier injection SCLC model [47, 48]. At high frequencies where the oscillation period probe signal is shorter than the transit time, the carriers injected by the probe signal cannot reach the steady-state space-charge distribution, which results in the observation of geometrical capacitance. Note that the mobility can be evaluated using the transit time in SCLC conditions [49] as follows

$$\mu = \frac{4}{3} \frac{d^2}{V_{\rm dc}} \frac{1}{t_{\rm tr}},\tag{1.7}$$

The transit time can be clearly estimated from maxima of the negative differential susceptance  $-\Delta B$ , since it is related to the frequency as

$$t_{\rm tr} = 0.72 \frac{1}{f_{\rm max}},\tag{1.8}$$

as it is shown in Fig. 1.9. A similar approach has also been applied to OLEDs [50], organic solar cells [51], and OFETs [52].

Fig. 1.9. The impedance spectroscopy setup and the frequency dependence of the capacitance and negative differential susceptance  $-\Delta B$ .

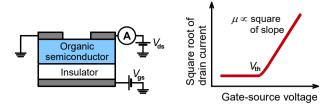

The organic field-effect transistor (OFET) mobility is a very important parameter since the charge transport in the OFET device occurs at the organic semiconductor/gate insulator interface. Since the high density of accumulated charge carriers and high electric fields make outstanding interface transport, the mobility is often denoted as the "field-effect mobility". The charge accumulation and transport across the channel region can be modelled in the saturated region using gradual channel approximation [53-55]; hence, the drain-source current  $I_{\rm ds}$  is a linearly dependent on the gate-source voltage  $V_{\rm gs}$  and follows relation

$$I_{\rm ds} = C_{\rm g} \mu \frac{W}{2L} (V_{\rm gs} - V_{\rm th})^2,$$

(1.9)

where  $C_g$  is the capacitance per unit of area,  $V_{th}$  is the threshold voltage, W and L are channel width and channel length, respectively. As a result, the field-effect mobility can be estimated from a slope as

$$\mu = \frac{2L}{wc_{\rm g}} \left(\frac{\partial I_{\rm ds}^{1/2}}{\partial V_{\rm gs}}\right)^2,\tag{1.10}$$

as depicted in Fig. 1.10. Considering straightforward evaluation of the field-effect mobility, the OFET technique is used as a benchmark for a mobility evaluation. It should be mentioned here that the field-effect mobility estimation is burdened with error originating in the imperfect ohmic contacts, short-channel effect, or electric-field dependence (the Poole-Frenkel effect).

Fig. 1.10. The OFET setup and output characteristic used for the field-effect mobility evaluation.

### 1.3. Organic Field-Effect Transistor (OFET)

### 1.3.1. History of OFET

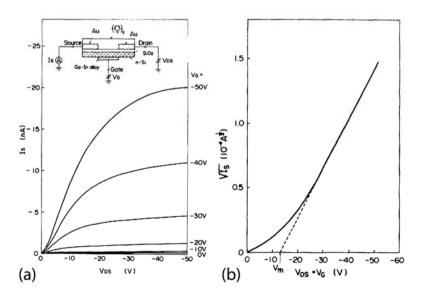

The first transistor was discovered in 1947 in Bell Laboratories in the USA. For the discovery of the transistor, its inventors received the 1956 Nobel Prize in Physics. The original idea behind the creation of a field-effect transistor (FET) originated in the mid-1920s. The first concept of the metal-oxide-semiconductor field-effect-transistors (MOSFET) was demonstrated finally in 1960 [56]. Later in 1977, scientists MacDiarmid, Heeger and Shirakawa published the electrical conductivity of the polymer polyacetylene (PA), and in 2000 gained the Nobel Prize in Chemistry [57]. The last milestone on the way to the first organic transistor was 1986 when scientists Tsumura, Koezuka and Ando succeeded in developing the first field-effect transistor using polythiophene as a semiconductor layer [2]. The transistor structure of the first organic field-effect transistor (OFET) as well as its output and transfer characteristics, are shown in Fig. 1.11.

**Fig. 1.11.** (a) Output and transfer characteristics of the first OFET using polythiophene as a semiconductor layer. Reprinted from A. Tsumura, H. Koezuka, and T. Ando, *Applied Physics Letters*, Vol. 49, 1986, 1210, with the permission of AIP Publishing.

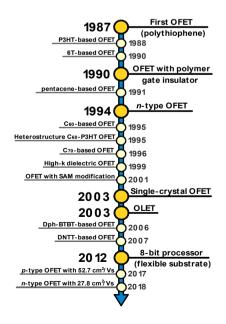

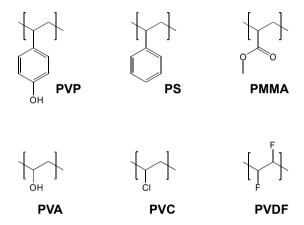

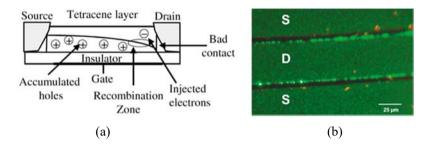

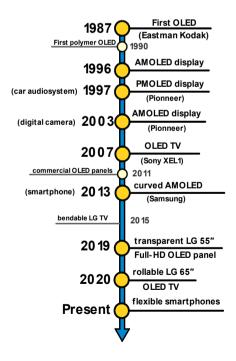

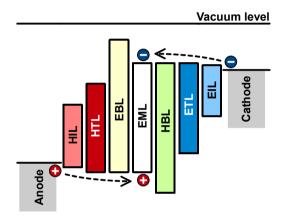

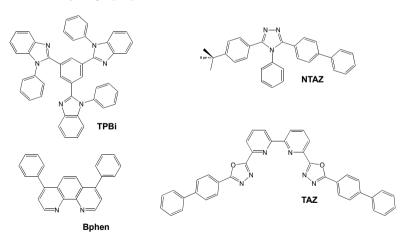

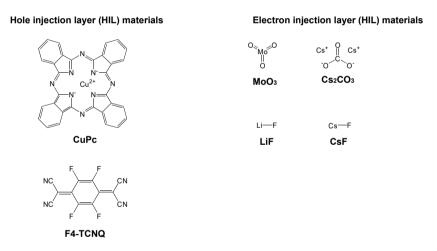

Even though the first OFET device was discovered in 1986 [2], there was an abrupt and rapid evolution of OFET devices and related materials. Fig. 1.12 illustrates the timeline of the research progress. In 80's has been introduced well-known materials such as poly(3-hexylthiophene-2.5-divl) (P3HT) and sexithiopene (6T) [58, 59]. Very first devices were very uncomplicated and utilized an inorganic gate insulator layer. The first polymer gate insulator was proposed in 1990 and applied CYEPL, PVA, PVC, PMMA, PSt polymers [60]. Pentacene is a famous semiconductor nowadays, but its journey began in 1991 [61]. Interestingly, all these devices exhibited p-type conductivity, and the electron conductive materials were beyond the scope of organic electronics. The n-type OFET device was reported in 1994 by Brown et al. and used TCNQ as an active layer [62]. The most well-known *n*-type semiconductor, fullerene C<sub>60</sub>, was suggested one year later, in 1995 [63]. Since fullerene was a very perspective material with relatively high electron mobility, various applications were introduced, such as pn heterostructures [64]. Besides fullerene C<sub>60</sub> other fullerene-based materials were characterized in the next years [65]. Also, modification of the gate insulator or injection electrodes took place in the late '90s [66]. Surprisingly, the holy grail of microelectronics, the single-crystal semiconductor, was accomplished in 2003 using rubrene [67]. Although the electron properties were significantly better, the research remained focused on polycrystalline devices. In the same year, the tetracene-based organic light-emitting transistor (OLET) shined a light [68]. Among aromatic rings, the thienoacenes and thiophene benzene fused compounds such as DNTT and BTBT were introduced in OFET devices in 2006-2007 [69, 70]. Almost immediately, they began popular due to the high effective mobility. The first 8-bit processor deposited on the flexible substrate was demonstrated in 2012 to illustrate the capability of the technology [71]. Later, the novel organic semiconductors and optimization of deposition techniques lead to the hole and electron mobility as high as 52.7 and 27.8 cm<sup>2</sup>/V.s [72, 73].

Fig. 1.12. The timeline of OFET evolution.

### 1.3.2. How the OFET Works?

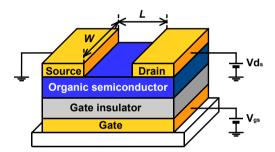

The structure of OFET is very similar to thin-film transistors based on inorganic materials in the metal-oxide-semiconductor structures (MOSFET). The three-dimensional geometry of the most common and fundamental structure, known as top contact – bottom gate organic field-effect transistor, is depicted in Fig. 1.13. OFET in this structure consists of two thin-film layers – dielectric and organic semiconductor layer and three metal electrodes – source, drain and gate. The active charge-transport layer consists of a thin-film organic semiconductor with source and drain electrodes. The conductive channel in the OFET device is created in the organic semiconductor layer, especially at the semiconductor/gate insulator interface. The gate insulator layer can be fabricated of organic as well as inorganic materials. The most important is to satisfy the requirements on low leakage currents (*i.e.* gate insulator must have a high electrical resistance). Source and drain electrodes are mainly formed of metal layers. The electrode deposition can be done by the thermal evaporation in a vacuum, the printing techniques (*e.g.* inkjet printing or screen printing), or even by mechanical lamination.

Fig. 1.13. Schematic drawing of the OFET structure in a top contact – bottom gate configuration.

The conductive channel is formed between the source and drain electrodes through an organic semiconductor if the appropriate voltage is applied to the gate electrode. In the case of OFET devices, the channel length *L* between the source and drain electrodes is usually in the order of hundreds of micrometres, whereas the width *W* is greatly larger and varies from millimetres to centimetres. In general, the channel/width length is limited by the fabrication technology, *i.e.* dimensions of the shadow mask used during the metal evaporation or printing resolution [8, 74]. The gate electrode potential controls the accumulation layer on the semiconductor/gate insulator interface that is crucial for the current flow between the source and drain electrodes. Hence, OFET can be used in a wide range of electronic systems as a switching device. The fundamental relations describing the current-voltage characteristics of OFET are identical to the already known Shockley's equations describing the metal-oxide-silicon field-effect transistors (MOS FETs) [53].

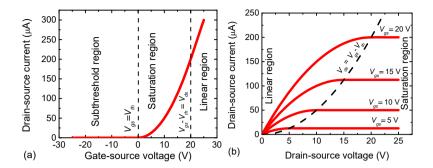

Regarding the applied gate-source voltage, we recognise several regions in the current-voltage characteristics. If the gate-source voltage  $V_{\rm gs}$  is greatly lower than the threshold voltage  $V_{\rm th}$ , the OFET device is closed, and only a low level of the off-current is observed. Increasing the gate-source voltage  $V_{\rm gs}$  will its value approaches the threshold

voltage, the device is in the *subthreshold region*, and it is starting to turn on. The current is very low, but it rises in an exponential way. Above the threshold region,  $V_{\rm gs} > V_{\rm th}$ , the conductive channel is formed between the source and drain electrodes; however, due to the low electric field, it is still limited by the bottleneck denoted as pinch-off, and the drain-source current is conserved even though the drain-source voltage  $V_{\rm ds}$  is increased. Since the output current is saturated, we recognise this voltage region as a *saturated* one. The increase of gate-source  $V_{\rm gs}$  voltage greatly above drain-source voltage  $V_{\rm ds}$  gives a rise of the highly conductive channel, and the organic semiconductor exhibits Ohmic behaviour. Considering linear current dependence on the applied voltage, the Ohmic character, the voltage region is identified as a *linear* one. Furthermore, the drain-source current dependence on the drain-source voltage represents the output current reliance; hence, it is named the *output characteristic*. On the other hand, the drain-source current dependence on the gate-source voltage demonstrates the transfer nature of the switching device; therefore, it is recognised as a *transfer characteristic*.

To express the nature mentioned above of OFET devices is used the gradual channel approximation proposed by Shockley. This theory approximates the charge transport in one dimension, assuming the separation of the source-drain electrodes greatly larger than the gate-source electrode separation. In other words, it requires channel length greatly larger than the film thicknesses (organic semiconductor and gate insulator films). Subsequently, if the conductive channel is formed (linear region) the drain-source current  $I_{\rm ds}$  can be expressed as

$$I_{\rm ds} = \frac{WC_{\rm g}}{L} \mu \left( V_{\rm gs} - V_{\rm th} - \frac{1}{2} V_{\rm ds} \right) V_{\rm ds},$$

(1.11)

where  $C_{\rm g}$  and  $\mu$  stand for the material parameters, namely the gate insulator capacitance per unit of area and the charge mobility in an organic semiconductor, respectively. The gate capacitance includes material properties and geometry of gate insulator layer,  $C_{\rm g} = \varepsilon_0 \varepsilon_{\rm r}/d$ , where  $\varepsilon_0 \varepsilon_{\rm r}$  and d are the dielectric constant and the thickness of the gate insulator. It also means that with the reduction of dielectric insulator thickness or the rise of relative permittivity, the capacity increases and the drain-source current also grows up. It should be noted here that this relation is valid for the high gate-source voltage only,  $V_{\rm ds} < V_{\rm gs} - V_{\rm th}$ , whereas for low gate-source voltages (saturated region),  $V_{\rm ds} > V_{\rm gs} - V_{\rm th}$ , the relation is simplified,

$$I_{\rm ds} = \frac{w c_{\rm g}}{2L} \, \mu \, (V_{\rm gs} - V_{\rm th})^2$$

(1.12)

The output and transfer characteristics, Fig. 1.14, offer the possibility of extracting the basic parameters of the transistor. The material parameters related to the organic semiconductor, especially the mobility and the threshold voltage. The mobility can be evaluated from the transfer characteristics by modifying the equation (1.12) as follows

$$\mu = \frac{2L}{WC_{\rm g}} \left(\frac{\partial I_{\rm ds}^{1/2}}{\partial V_{\rm gs}}\right)^2 \tag{1.13}$$

**Fig. 1.14.** Typical (a) transfer, and (b) output characteristics of OFET. Basic operation regions are also denoted.

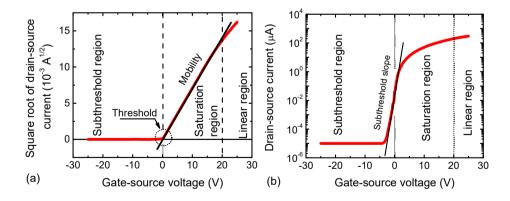

Demonstration of the threshold voltage and mobility evaluation is shown in Fig. 1.15 (a). Another parameter describing the transistor's quality as the switching device is the ratio of the output currents in the on-state and the off-state, so-called on/off ratio (see Fig. 1.15 (b)). It defines the difference between the open and closed channel and plays a key role in logic circuits or active matrix display organic light-emitting diode backplanes. Even though the OFET devices cannot offer mobility as high as silicon-based FETs, the channel can be properly closed, and the on/off ratio usually reaches the level from 10<sup>5</sup> up to 10<sup>8</sup>. The channel transconductance is used to evaluate conductive channel properties from the transfer characteristic

$$g_{\rm m} = \left(\frac{\partial I_{\rm ds}}{\partial V_{\rm gs}}\right)_{V_{\rm ds}} \tag{1.14}$$

**Fig. 1.15.** Other plots of the output characteristics. (a) Square-root plot for estimation of the mobility and the threshold voltage in the saturated region; (b) Semi-log scale for evaluation of the subthreshold slope in the subthreshold region.

Especially, it is a powerful tool in the subthreshold region, where the current rises exponentially, Fig. 1.15 (b). In details, the semi-log scale of the output characteristic in

the subthreshold region is linear, and the subthreshold slope can be estimated. The subthreshold slope expresses how abrupt is the transition from the off-state to the on-state. Notably, the subthreshold slope's reciprocal value, the so-called subthreshold swing, is commonly used since it clearly describes the voltage required to increase the current by one decade (V/dec).

### 1.3.3. OFET Architecture

The OFET device architecture is distinguished in accordance with current flow and the electrode geometry. Since the OFET devices are thin-film structure deposited on the planar solid substrate, the current flow can be in the plane of the substrate, the horizontal architecture, or in the normal direction, the horizontal architecture.

### 1.3.3.1. Horizontal Architecture

### Top contacts

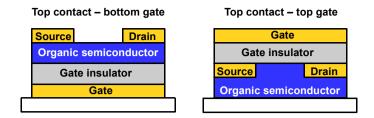

Top contact geometries are defined by the deposition of source/drain contacts on the top of the organic semiconductor layer. In other words, the organic semiconductor is deposited on the substrate, and source/drain electrodes are formed subsequently. The bottom electrode can be situated under the organic semiconductor, the top contact – bottom gate geometry, or above the organic semiconductor, the top contact – top gate geometry, see Fig. 1.16.

The device geometry selection defines a requirement on the electrode fabrication technology to avoid organic semiconductor damage. There are various common options for the gate electrode materials, such as metals or metal oxides. Metal layers provide high conductivity, while the metal oxide (e.g. indium tin oxide or doped zinc oxide) offer optical transparency. If the gate electrode is deposited as a continuous layer, the pattering technique, like laser ablation or photolithography, is necessary. For organic semiconductor testing, the highly doped silicon wafer with thermal oxide is applied as a gate electrode with a gate insulator layer even though this approach has no industrial application.

The advantages of this geometry are relatively simple fabrication and significantly lower contact resistance due to the penetration of the metal used for the electrodes into the organic semiconductor layers. The second approach, the top contact – top gate geometry, is based on the deposition of the organic semiconductor layer directly on the substrate. The source and drain electrodes deposited on the organic layer are covered with a gate insulator layer. Finally, the gate electrode is formed on the top, Fig. 1.16 (b) [75, 76]. Although the top contact – top gate needs more complex design and fabrication technology limitations, it offers an advantage of device encapsulation.

**Fig. 1.16.** The OFET horizontal architectures with top contact – bottom gate or top contact – top gate geometry.

#### **Bottom contacts**

In the bottom contact geometry, the source and drain electrodes are deposited prior to the organic semiconductor, Fig. 1.17. The obvious advantage of this geometry is the possibility of fine electrode patterning technique application. In details, the photolithography process can be utilised to fabricate devices with short channels without the risk of organic semiconductor degradation. On the other hand, the bottom contacts lead to greatly higher contact resistance as well as nonlinear dependence of the drain-source current at low drain-source voltages. This phenomenon causes nonlinear series resistance between the source and drain electrodes [77]. Similar to the top contact approach, also here, we meet the possibility of the top gate geometry [78].

**Fig. 1.17.** The OFET horizontal architectures with bottom contact – bottom gate or bottom contact – top gate geometry.

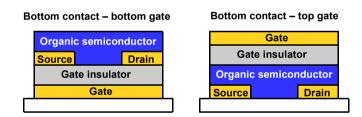

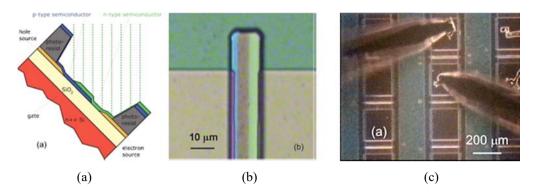

#### 1.3.3.2. Vertical Architecture

Till now, we discussed OFET devices with charge transport in the plane of the substrate, the horizontal geometry. Another alternative design offers the charge transport in the normal direction, the vertical architecture. Therefore, the channel length is in a sandwich-like structure defined by the thickness of the organic semiconductor layer that separates the source and drain electrodes. Here, the gate electrode is located between the source and drain electrodes or beside the channel. The advantages of vertical architecture are short channels offering fast devices and large electrode areas providing high output current [79]. Various designs of OFET with vertical architecture have been proposed in the last two decades, see Fig. 1.18.

**Fig. 1.18.** Vertical structures of organic transistors: (a) Organic SIT; (b) Vertical OFET; (c) Vertical-channel organic field-effect transistor; (d) Step-edge vertical-channel organic field-effect transistor.

## **Organic static induction transistor (OSIT)**

This type of vertical OFET geometry was first proposed by Kudo [80] as an analogy to an inorganic SIT transistor. In this design, the charge carriers are transported through an organic semiconductor layer sandwiched between the source and drain electrodes, while the current is controlled by a grid-shaped gate electrode located in the centre of the organic semiconductor layer, as shown in Fig. 1.18(a). However, due to the resulting leakage currents at higher gate-source voltages and the extremely low on/off current ratio, this geometry is not widely used. The uncomplicated structure of OSIT and the absence of a gate insulator allows us to create a transistor easily, even on a flexible substrate. This means that OSIT can be produced by a thermal evaporation deposition (PVD) in a single run, without the need of breaking the vacuum [80].

### **Vertical organic field-effect transistor (VOFET)**

Vertical OFET device consists of two parts: the diode (source/organic semiconductor/drain) and the capacitor (source/insulating layer/gate), whereas the source electrode is common for diode and capacitor, Fig. 1.18(b). For correct function must be fulfilled two main conditions: (i) high capacity of the capacitor and (ii) non-continuous or patterned source electrodes. The very first devices used a non-continuous metal layer as a source electrode [81], whereas later, the patterned grid structure was used. As a result, the vertical OFET in such a structure behaves like a diode where the injection electrode can be expanded by the application of gate-source voltage [82, 83].

## Vertical-channel organic field-effect transistor

A key feature of a vertical-channel OFET is the short length of the channel, which is defined by the thickness of the gate insulator layer located between the source and drain

electrodes, similar to horizontal OFET architecture. After deposition of the source and drain electrodes, between which is deposited a dielectric layer, the entire layer is chemically patterned or stamped in the design of a letter V. Subsequently, a layer of organic semiconductor, a second insulator layer and a gate electrode are deposited. These layers copy the previously patterned surface morphology, as shown in Fig. 1.18(c). The resulting channel length is usually around 1  $\mu$ m, while the shorter channel would suffer an increased leakage current breaking through the dielectric layer between the source and drain electrodes [84, 85].

## Step-edge vertical-channel organic field-effect transistor (SVC OFET)

This device geometry is also known as the three-dimensional OFET, is created on a patterned substrate to create a sharp edge, Fig. 1.18 (d). Subsequently, the gate electrode, the dielectric layer and the organic semiconductor are deposited. In the last step, the top electrodes, source and drain, are formed by deposition of the metal under an inclined angle; hence the shadow defines the channel region. In this approach, the edge of the substrate serves as a shadow mask, whereas the channel is formed along the sidewall of the edge [86].

#### 1.3.4. Materials

#### **1.3.4.1. Substrates**

Even though there are many types of OFET substrates, we can divide them into two major categories: organic (polymer) and inorganic substrates. Typical examples of polymer substrates are polyethylene naphthalate (PEN), polyethylene terephthalate (PET), polyethylene (PE) and polyimide (PI). Polymer substrates are flexible and lightweight. Some polymers such as PEN, PET, and PI also have sufficient thermal resistance, so these are suitable as substrates of OFETs. On the other hand, inorganic substrates such as glass, quartz, and silicon wafer excel over polymer substrates by their high melting point, lower surface roughness and lower diffusivity of chemicals or air. Substrate such as heavily-doped silicon (Si) wafer is widely used as gate electrodes for organic semiconductor testing [87].

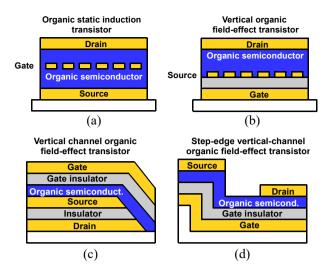

## 1.3.4.2. Insulator Layer

Even though the organic semiconductor had been applied in organic field-effect transistor from the early beginning, the organic gate insulators did not reach an acceptable level, and inorganic insulators were applied for early-stage devices. The first polymer insulator layer applied in the OFET device was used in 1990 [60, 88]. Since 1990, a large number of different insulating materials have been investigated. Material research has focused on inorganic, organic, or organic-inorganic hybrid materials to create high-capacity thin layers with low leakage currents. The second requirement was simple deposition and compatibility with organic semiconductors or metal electrodes. The gate insulator layer in the OFET device is mostly sandwiched between the gate electrode and the organic

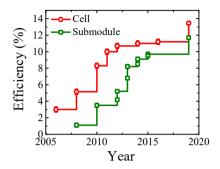

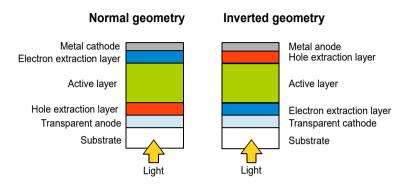

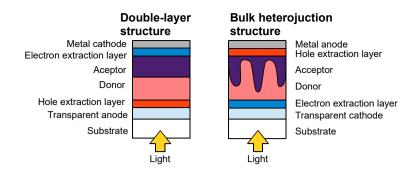

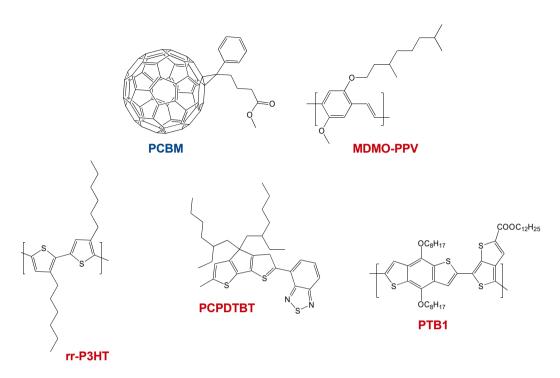

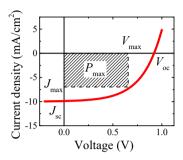

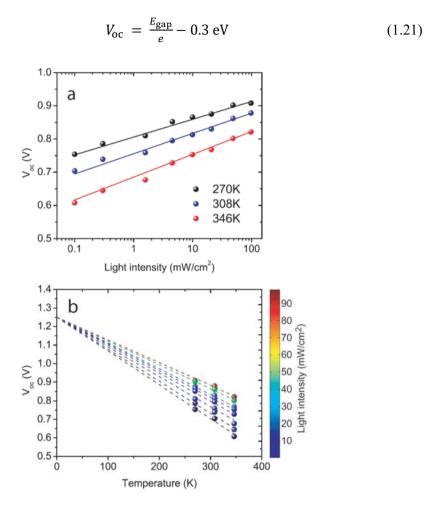

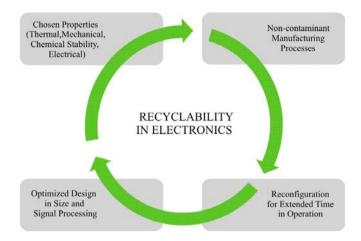

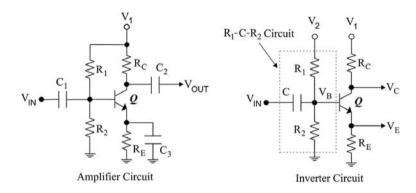

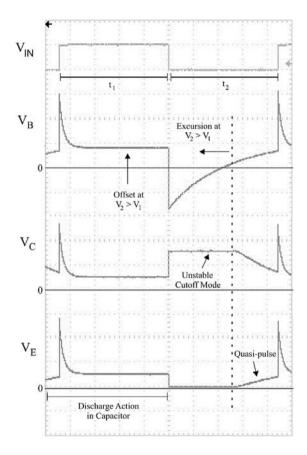

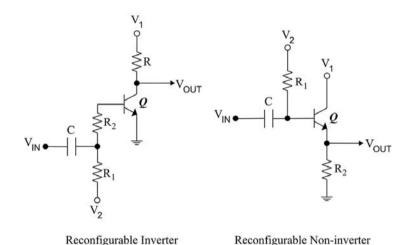

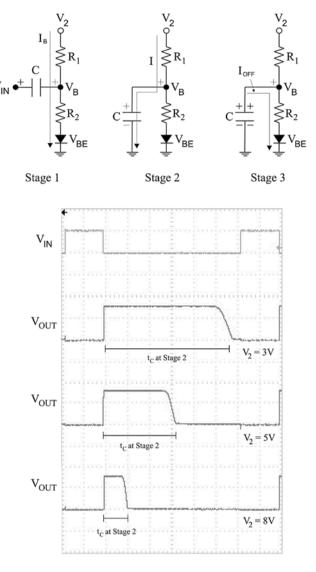

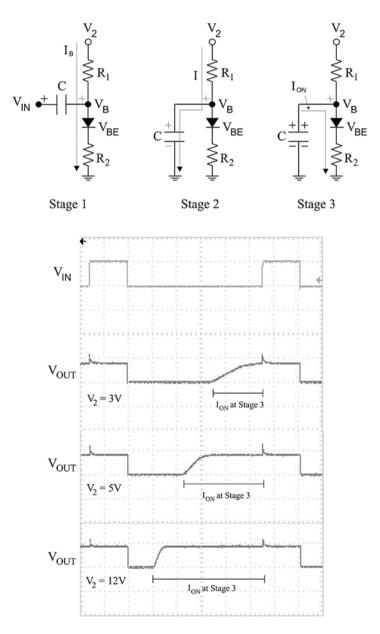

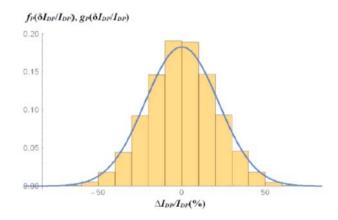

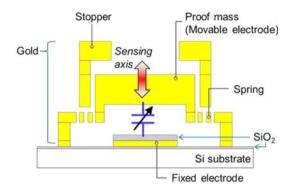

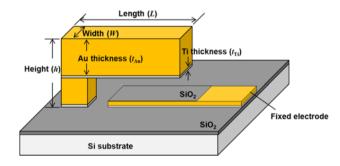

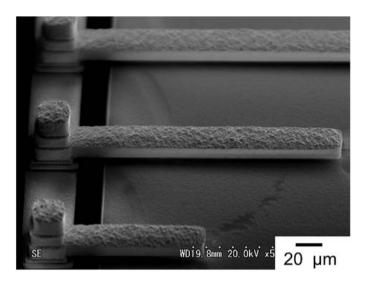

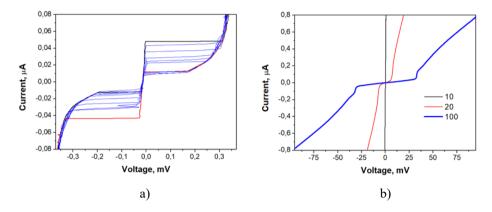

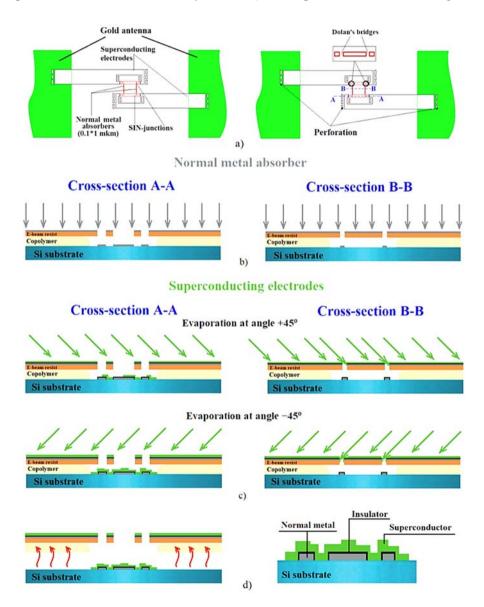

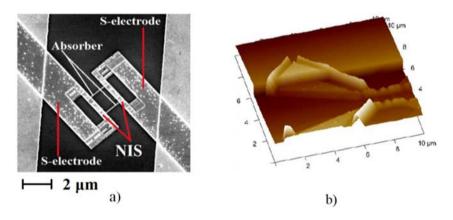

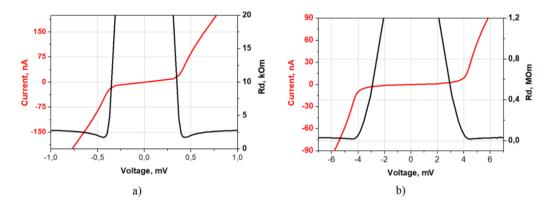

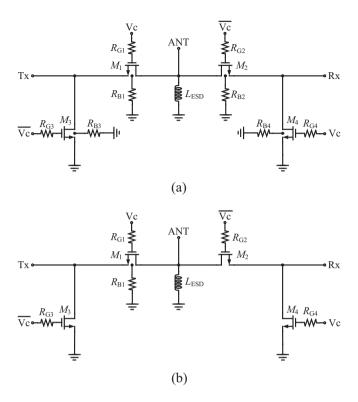

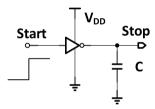

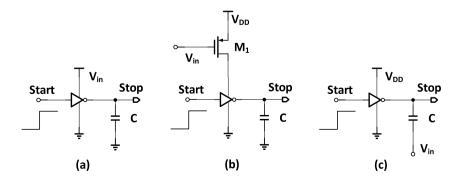

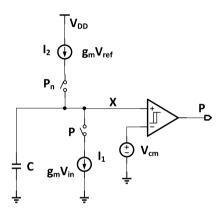

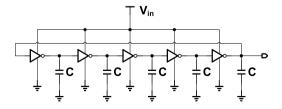

semiconductor. This structure creates two interfaces (gate electrode/gate insulator and gate insulator/organic semiconductor) with different requirements. Furthermore, it is necessary to cover the gate electrode perfectly to avoid high leakage current via pinholes.